신호 처리를위한 AD9959 기능 이해

AD9959는 강력하고 유연한 디지털 신시사이저로 4 개의 독립적 인 채널에서 주파수, 위상 및 진폭을 제어 할 수 있습니다.이 기사는 AD9959의 주요 기능, 기술 사양 및 공통 응용 프로그램을 다루 므로이 장치를 다양한 설정에서 사용하는 방법을 쉽게 이해할 수 있습니다.AD9959는 민첩한 로컬 발진기를 만들거나 단계적 배열 레이더와 같은 복잡한 시스템을 동기화하려는 경우 광범위한 프로젝트에 필요한 정밀도와 적응성을 제공합니다.이 가이드가 끝날 무렵, AD9959의 작동 방식과 다른 필드에 어떻게 적용되는지에 대한 명확한 이해를 얻을 수 있습니다.목록

AD9959의 개요

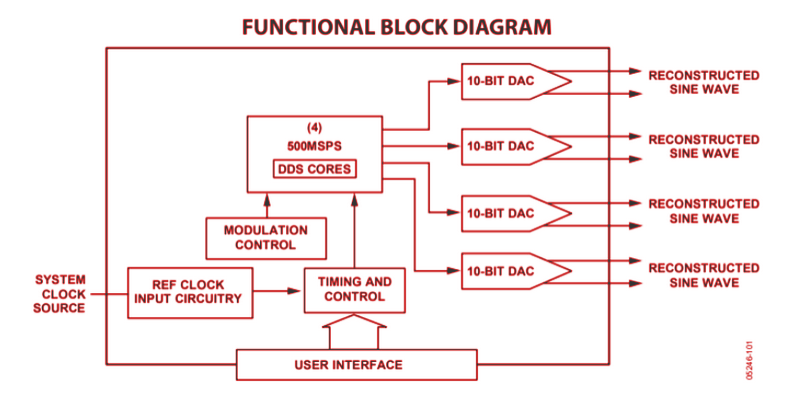

그만큼 AD9959 4 개의 직접 디지털 신시사이저 코어를 제공하여 각 채널에 대해 주파수, 위상 및 진폭을 독립적으로 제어 할 수 있습니다.주파수, 위상 또는 진폭 등 최대 16 개의 변조 수준의 변조를 처리 할 수 있으므로 설계에 유연성을 제공합니다.모든 채널은 동일한 시스템 시계를 공유하므로 동기화되어 여러 채널에서 원활한 작동을 보장합니다.또한 둘 이상의 AD9959로 작업하는 경우 여러 장치를 쉽게 동기화하여 복잡한 설정에 이상적입니다.

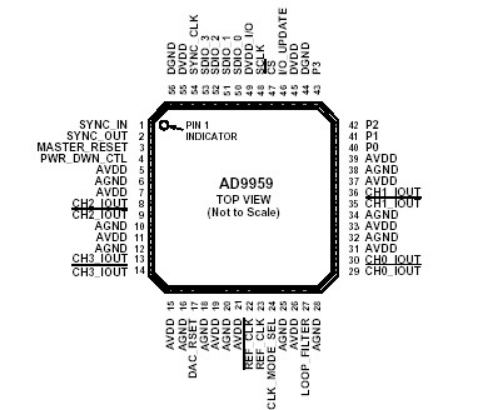

AD9959 핀아웃 다이어그램

| 핀 번호 | 니모닉 | I/O | 설명 |

| 1 | sync_in | 나 | 여러 AD9959 장치를 동기화하는 데 사용됩니다.마스터 AD9959 장치의 SYNC_OUT 핀에 연결합니다. |

| 2 | sync_out | 영형 | 여러 AD9959 장치를 동기화하는 데 사용됩니다.슬레이브 AD9959 장치의 SYNC_IN 핀에 연결합니다. |

| 3 | Master_reset | 나 | 활성 높은 재설정 핀.Master_Reset 핀을 주장하면 AD9959 내부 레지스터가 기본 상태로 향합니다. |

| 4 | pwr_dwn_ctl | 나 | 외부 전원 다운 제어. |

| 5, 7, 11, 15, 19, 21, 26, 31, 33, 37, 39 | AVDD | 나 | 아날로그 전원 공급 장치 핀 (1.8V). |

| 6, 10, 12, 16, 18, 20, 25, 28, 32, 34, 38 | agnd | 나 | 아날로그 그라운드 핀. |

| 44, 56 | DVDD | 나 | 디지털 전원 공급 장치 핀 (1.8V). |

| 45, 55 | dgnd | 나 | 디지털 파워 그라운드 핀. |

| 8 | CH2_IOUT | 영형 | 진정한 DAC 출력.AVDD로 종료됩니다. |

| 9 | CH2_IOUT | 영형 | 보완적인 DAC 출력.AVDD로 종료됩니다. |

| 13 | CH3_IOUT | 영형 | 진정한 DAC 출력.AVDD로 종료됩니다. |

| 14 | CH3_IOUT | 영형 | 보완적인 DAC 출력.AVDD로 종료됩니다. |

| 17 | dac_rset | 나 | 모든 DAC에 대한 참조 전류를 설정합니다.1.91 kΩ 저항 (공칭)은 핀 17에서 AGND로 연결됩니다. |

| 22 | ref_clk | 나 | 보완 참조 클록/발진기 입력.ref_clk가 단일 끝 모드에서 작동되면이 핀은 0.1 µF 커패시터가있는 AVDD 또는 AGND로 분리되어야합니다. |

| 23 | ref_clk | 나 | 참조 클록/발진기 입력.ref_clk가 단일 엔드 모드에서 작동하면 입력입니다.참조 클록 구성에 대한 작동 모드 섹션을 참조하십시오. |

| 핀 번호 | 니모닉 | I/O | 설명 |

| 24 | clk_mode_sel | 나 | 발진기 섹션의 제어 핀.주의 :이 핀을 1.8V 이상으로 구동하지 마십시오.높은 (1.8V) 인 경우, 오실레이터 섹션은 REF_CLK 소스로서 크리스탈을 허용 할 수있게됩니다.낮은 경우 발진기 섹션이 우회됩니다. |

| 27 | loop_filter | 나 | PLL 루프 필터의 외부 제로 보정 네트워크에 연결합니다.일반적으로 네트워크는 AVDD에 묶인 680pf 커패시터와 직렬로 0Ω 저항으로 구성됩니다. |

| 29 | CH0_IOUT | 영형 | 보완적인 DAC 출력.AVDD로 종료됩니다. |

| 30 | CH0_IOUT | 영형 | 진정한 DAC 출력.AVDD로 종료됩니다. |

| 35 | CH1_IOUT | 영형 | 보완적인 DAC 출력.AVDD로 종료됩니다. |

| 36 | CH1_IOUT | 영형 | 진정한 DAC 출력.AVDD로 종료됩니다. |

| 40 ~ 43 | P0 ~ P3 | 나 | 변조에 사용되는 데이터 핀 (FSK, PSK, ASK), 스위프 축적기를 시작/중지하거나 출력 진폭을 증가 시키거나 램프 하락하는 데 사용됩니다.데이터는 SYNC_CLK (핀 54)와 동기입니다.데이터 입력은 SYNC_CLK의 설정 및 시간 요구 사항을 유지해야합니다.이 핀의 기능은 프로파일 핀 구성 (PPC) 비트 (FR1 [14:12])에 의해 제어됩니다. |

| 46 | i/o_update | 나 | 상승 에지는 직렬 I/O 포트 버퍼에서 활성 레지스터로 데이터를 전송합니다.I/O_UPDATE는 SYNC_CLK (핀 54)와 동기입니다.I/O_UPDATE는 DAC 출력에 대한 데이터의 고정 파이프 라인 지연을 보장하기 위해 SYNC_CLK의 설정 및 시간 요구 사항을 유지해야합니다.그렇지 않으면, 파이프 라인의 ± 1 sync_clk 불확실성이 존재합니다.최소 펄스 폭은 하나의 SYNC_CLK 기간입니다. |

| 47 | CS \ | 나 | 활성 로우 칩 선택.여러 장치가 공통 I/O 버스 (SPI)를 공유 할 수 있습니다. |

| 48 | SCLK | 나 | I/O 운영의 직렬 데이터 클럭.데이터 비트는 SCLK의 상승 가장자리에 작성되었으며 SCLK의 하락 가장자리에서 읽습니다. |

| 49 | DVDD_I/O | 나 | 3.3V SPI 포트 및 디지털 I/O 용 디지털 전원 공급 장치. |

| 50 | sdio_0 | I/O | 데이터 핀 SDIO_0은 직렬 포트 I/O 전용입니다. |

| 51, 52 | sdio_1, sdio_2 | I/O | 데이터 핀 SDIO_1 및 데이터 핀 SDIO_2는 직렬 I/O 포트에 사용하거나 DAC 출력 진폭의 램프 업/램프 다운 (RU/RD)을 시작하는 데 사용될 수 있습니다. |

| 53 | sdio_3 | I/O | 데이터 핀 SDIO_3은 직렬 I/O 포트에 사용하거나 DAC 출력 진폭의 램프 업/램프 다운 (RU/RD)을 시작할 수 있습니다.단일 비트 또는 2 비트 모드에서 SDIO_3은 SYNC_I/O에 사용됩니다.SYNC_I/O 함수가 사용되지 않으면 접지 또는 논리에 묶으십시오. SDIO_3을 단일 비트 또는 2 비트 모드로 플로팅하지 마십시오. |

| 54 | sync_clk | 영형 | SYNC_CLK는 시스템 시계 속도의 4 분의 1로 실행됩니다.비활성화 될 수 있습니다.I/O_UPDATE 또는 DATA (PIN 40 ~ PIN 43)는 SYNC_CLK와 동기입니다.DAC 출력에 대한 데이터의 고정 파이프 라인 지연을 보장하려면 I/O_UPDATE 또는 데이터 (핀 40 ~ 핀 43)는 설정을 충족하고 SYNC_CLK의 상승 에지에 대한 시간 요구 사항을 유지해야합니다.그렇지 않으면, ± 1 sync_clk 불확실성의 기간이 발생합니다. |

AD9959 CAD 모델 개요

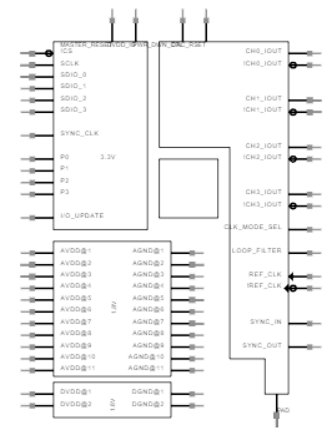

AD9959 기호

AD9959 발자국

자세한 AD9959 블록 다이어그램

AD9959 기술 사양

아날로그 장치 Inc. AD9959BCPZ의 기술 사양, 속성, 매개 변수 및 비슷한 부분.

| 유형 | 매개 변수 |

| 수명주기 상태 | |

| 공장 리드 타임 | 8 주 |

| 접촉 도금 | 주석 |

| 산 | 표면 마운트 |

| 장착 유형 | 표면 마운트 |

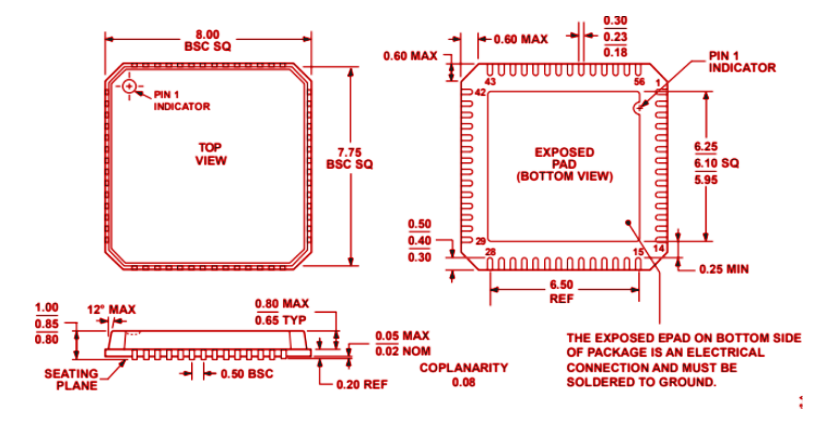

| 패키지 / 케이스 | 56-VFQFN 노출 패드, CSP |

| 핀 수 | 56 |

| 작동 온도 | -40 ° C ~ 85 ° C |

| 포장 | 쟁반 |

| JESD-609 코드 | E3 |

| pbfree 코드 | 아니요 |

| 부품 상태 | 활동적인 |

| 수분 감도 수준 (MSL) | 3 (168 시간) |

| 종료 수 | 56 |

| 종료 | smd/smt |

| ECCN 코드 | 귀 99 |

| 추가 기능 | 또한 3.3V 공급이 필요합니다 |

| 최대 전력 소산 | 680MW |

| 전압 - 공급 | 1.71V ~ 1.96V |

| 터미널 위치 | 쿼드 |

| 터미널 형태 | 리드가 없습니다 |

| 피크 리플 로우 온도 (° C) | 260 |

| 공급 전압 | 1.8V |

| 터미널 피치 | 0.5mm |

| 빈도 | 500MHz |

| 시간 @ 피크 리플 로우 온도 (S) | 30 |

| 기본 부품 번호 | AD9959 |

| 핀 수 | 56 |

| 자격 상태 | 자격이 없습니다 |

| 공급 전압 | 1.8V |

| 인터페이스 | 연속물 |

| 운영 공급 전류 | 180ma |

| 공칭 공급 전류 | 160ma |

| 최대 공급 전류 | 185ma |

| UPS/UCS/주변 ICS 유형 | |

| 비트 수 | 10 |

| 샘플링 속도 | 500msps |

| 경계 스캔 | 아니요 |

| 저전력 모드 | 예 |

| 전환율 | 500msps |

| D/A 변환기 수 | 4 |

| 해상도 (비트) | 10 b |

| 단어 너비 조정 (비트) | 32 b |

| 키 | 830μm |

| 길이 | 8mm |

| 너비 | 8mm |

| SVHC에 도달하십시오 | SVHC 없음 |

| ROHS 상태 | ROHS3 준수 |

| 무료로 리드 | 리드를 포함합니다 |

AD9959 주요 기능

4 500msps에서 4 개의 동기화 된 DDS 채널

AD9959는 4 개의 동기화 된 직접 디지털 신디사이저 (DDS) 채널을 제공하며, 모두 최대 500msps에서 작동합니다.이를 통해 동기화를 유지하면서 여러 채널에서 정확한 신호를 생성 할 수 있습니다. 이는 여러 출력이 원활하게 작동하는 프로젝트에서 작업 할 때 특히 유용합니다.

독립적 인 주파수, 위상 및 진폭 제어

4 개의 DDS 채널 각각은 주파수, 위상 및 진폭에 대한 독립적 인 제어를 제공합니다.이를 통해 다양한 요구에 맞게 각 채널을 미세 조정할 수 있으므로 다양한 신호 매개 변수를 처리 할 수있는 유연성을 제공합니다.

주파수, 위상 및 진폭 변화에 대한 일치하는 대기 시간

AD9959는 주파수, 위상 및 진폭의 변화가 채널에서 동기화되도록합니다.이는 하나의 매개 변수를 조정할 때 모든 채널에서 동시에 변경이 발생하여 지연없이 일관된 출력을 유지하는 데 도움이됩니다.

Excellent Channel-to-Channel Isolation

With over 65 dB of channel-to-channel isolation, the AD9959 minimizes interference between channels. This ensures that the signals generated on each channel are clean and distinct, providing a higher quality performance in your designs.

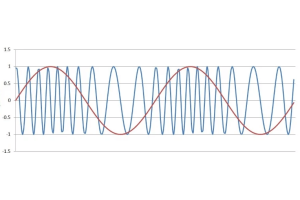

선형 스윕 기능

AD9959는 선형 주파수, 위상 및 진폭 스윕을 지원합니다.This feature allows you to smoothly transition between values, making it easier to generate signals that gradually change over time, which can be useful for testing and calibration purposes.

최대 16 개의 주파수, 위상 및 진폭 변조 수준

The device can handle up to 16 levels of modulation for frequency, phase, or amplitude. This level of flexibility enables you to implement a variety of modulation schemes, from simple to complex, depending on your project needs.

Integrated 10-bit Digital-to-Analog Converters (DACs)

Each channel comes with its own integrated 10-bit DAC, allowing you to convert digital signals into analog outputs with precision.이렇게하면 AD9959가 컴팩트 한 형태로 정확한 아날로그 신호 생성이 필요할 때 훌륭한 선택입니다.

개별적으로 프로그래밍 가능한 DAC 본격적인 전류

각 DAC의 전체 규모 전류를 개별적으로 프로그래밍 할 수 있으므로 각 채널의 출력 전력을 제어 할 수 있습니다.이 수준의 사용자 정의를 사용하면 특정 요구 사항에 따라 다른 채널의 전원 레벨을 최적화 할 수 있습니다.

미세 주파수 튜닝 해상도

AD9959는 0.12Hz 이상의 튜닝 해상도를 제공하여 생성하는 신호의 빈도를 정확하게 제어 할 수 있습니다.이 수준의 정확도는 작은 주파수 조정이 큰 차이를 만드는 응용 분야에서 작업 할 때 유리합니다.

고해상도 위상 오프셋

14 비트 위상 오프셋 해상도를 사용하면 AD9959를 사용하면 각 채널의 위상을 미세 조정할 수 있습니다.이 기능은 단계적 배열 시스템에서 다중 신호를 정렬 할 때와 같은 신호 간의 정확한 위상 조정이 필요할 때 도움이됩니다.

Output Amplitude Scaling

AD9959는 10 비트 출력 진폭 스케일링 해상도를 제공합니다.이를 통해 높은 정밀도로 출력 진폭을 조정하여 신호 강도를보다 정확하게 제어 할 수있는 유연성을 제공합니다.

Enhanced Serial I/O Port Interface

The serial I/O port interface (SPI) offers enhanced data throughput, allowing you to transfer data quickly and efficiently between the device and your system.이는 빠르게 진행되는 응용 프로그램에 유용 할 수있는 통신 속도를 높입니다.

전원 다운 제어

The AD9959 includes both software and hardware options for powering down, giving you control over how and when to save power.이 기능은 전력 효율이 우선 순위 인 에너지 의식 설계에 특히 유용합니다.

이중 공급 작업

이 장치는 DDS 코어의 경우 1.8V, 직렬 I/O의 경우 3.3V로 작동합니다.이 구성은 성능의 균형을 전력 요구와 균형을 잡아 다양한 설계 환경에 적응할 수 있도록 도와줍니다.

다중 장치 동기화

The AD9959 supports synchronization across multiple devices, allowing you to expand your design with additional units while maintaining precise timing between them.이를 통해 동기화를 잃지 않고 프로젝트를 쉽게 확장 할 수 있습니다.

선택 가능한 Refclk 승수

With a selectable REFCLK multiplier ranging from 4× to 20×, the AD9959 offers flexibility in clocking options, allowing you to choose the best setting for your design.

내장 RefClk 크리스탈 발진기

The device includes a built-in REFCLK crystal oscillator, which simplifies your design process by reducing the need for external components, making it easier to manage timing within the system.

Compact 56-lead LFCSP Package

AD9959는 56 리드 LFCSP 패키지로 제공되며 여러 DDS 채널을 설계에 통합하기위한 작고 공간 절약 옵션을 제공합니다.이 작은 폼 팩터는 보드 공간을 너무 많이 차지하지 않고 높은 기능성이 필요할 때 이상적입니다.

Common AD9959 Applications

Agile Local Oscillators

The AD9959 is well-suited for use in agile local oscillators, providing precise control over frequency, phase, and amplitude. This makes it a great option when you need flexible and adjustable signal generation in radio systems or other communications equipment.

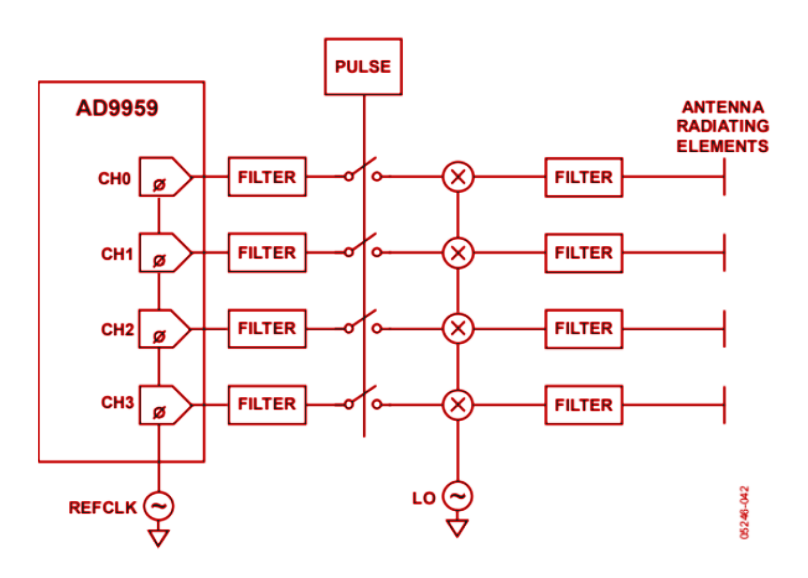

Phased Array Radars and Sonars

In phased array radar and sonar systems, precise synchronization of multiple signal channels is critical. The AD9959’s ability to handle independent control and synchronization across multiple channels makes it a perfect fit for these applications, ensuring accurate signal processing and timing.

수단

The AD9959 can be used in various types of instrumentation, particularly in devices that require precise signal generation and control. Whether it's for testing, measuring, or calibrating systems, the device's flexibility in adjusting frequency, phase, and amplitude adds versatility to your designs.

동기화 된 클럭

여러 채널에서 동기화 된 클럭킹이 필요한 프로젝트의 경우 AD9959는 훌륭한 솔루션을 제공합니다.Its built-in synchronization features allow you to maintain exact timing between channels, making it ideal for systems where timing accuracy is crucial.

RF Source for Acousto-Optic Tunable Filters (AOTF)

The AD9959 can act as an RF source for Acousto-Optic Tunable Filters (AOTF), providing reliable and precise signal generation for these optical systems. Its flexibility in frequency and amplitude control allows it to meet the demands of such specialized applications.

AD9959 Application Circuit Overview

AD9959 Dimension Outline Diagram

AD9959 제조업체 정보

Analog Devices has been a leading company in creating integrated circuits since 1965. The company specializes in designing and producing circuits that help convert, condition, and process signals from the real world—like temperature, sound, and motion—into electrical signals. These circuits are used in a wide range of electronic systems across the globe.

자주 묻는 질문 [FAQ]

1. What is the AD9959 used for?

The AD9959 contains four direct digital synthesizer (DDS) cores, each allowing independent control of frequency, phase, and amplitude on its respective channel.이 유연성은 PCB의 필터링, 증폭 또는 레이아웃 차이와 같은 아날로그 프로세스로 인한 신호의 불일치를 균형을 맞추는 데 도움이 될 수 있습니다.

2. How does the AD9959 work?

The AD9959 can modulate frequency, phase, or amplitude (using FSK, PSK, or ASK modulation) with up to 16 distinct levels. You control this modulation by applying signals to the profile pins, which allows the chip to switch between different modulation levels as needed.

우리에 대해

ALLELCO LIMITED

더 많은 것을 읽으십시오

빠른 문의

문의를 보내 주시면 즉시 응답하겠습니다.

TC7660COA 전압 변환기에 대한 포괄적 인 안내서

10월24일에서

TIP120 트랜지스터 이해

10월24일에서

인기있는 게시물

-

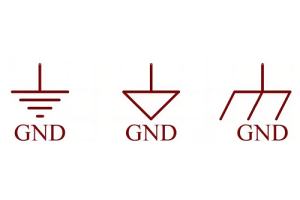

회로에서 GND는 무엇입니까?

1월1일에서 2925

-

RJ-45 커넥터 가이드 : RJ-45 커넥터 색상 코드, 배선 체계, R-J45 응용 프로그램, RJ-45 데이터 시트

1월1일에서 2484

-

파이버 커넥터 유형 : SC 대 LC 및 LC 대 MTP

1월1일에서 2075

-

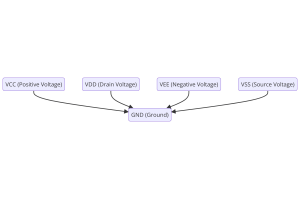

전자 제품 VCC, VDD, VEE, VSS 및 GND의 전원 공급 장치 이해

11월8일에서 1863

-

DB9와 RS232의 비교

1월1일에서 1757

-

LR44 배터리는 무엇입니까?

유비쿼터스 힘 인 전기는 사소한 기기에서 생명을 위협하는 의료 장비에 이르기까지 일상 생활의 모든 측면에 조용히 스며 들어 침묵하는 역할을합니다.그러나이 에너지, 특히 저장하고 효율적으로 출력하는 방법을 진정으로 파악하는 것은 쉬운 일이 아닙니다.이 기사는 표면에 중요하지 않은 것처럼 보일 수 있지만 실제 응용 분야, 즉 LR44 배터리에서 매우 다재다능한 코인 셀 배터리 유형에 초점을 맞출 것입니다.이 기사는 ...1월1일에서 1706

-

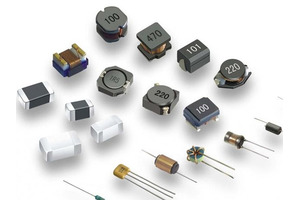

기본 이해 : 인덕턴스 저항 및 정관

전기 공학의 복잡한 춤에서, 기본 요소의 트리오는 인덕턴스, 저항 및 커패시턴스와 같은 중심 단계를 차지합니다.각각은 전자 회로의 역동적 인 리듬을 지시하는 독특한 특성을 나타냅니다.여기서 우리는 이러한 구성 요소의 복잡성을 해독하고 광대 한 전기 오케스트라 내에서 뚜렷한 역할과 실용적인 용도를 발견하기위한 여정을 시작합니다.자기 플럭스 마법사와 함께 인덕턴스;저항, 전류 흐름의 확고한 게이트 키퍼;그리고 ...1월1일에서 1649

-

CR2430 배터리 종합 가이드 : 사양, 응용 프로그램 및 CR2032 배터리 비교

CR2430 배터리는 무엇입니까?CR2430 배터리의 이점표준CR2430 배터리 애플리케이션CR2430 동등한CR2430 대 CR2032배터리 CR2430 크기CR2430 및 이와 동등한 것을 구입할 때 찾아야 할 사항데이터 시트 PDF자주 묻는 질문 배터리는 소형 전자 장치의 핵심입니다.사용 가능한 많은 유형 중에서 코인 셀은 일반적으로 계산기, 리모컨 및 시계에서 발견되는 중요한 역할을합니다.작은 크기에도 불구하고 각 코인 셀에는 독특한 장점이 ...1월1일에서 1536

-

RF는 무엇이며 왜 우리는 그것을 사용합니까?

무선 주파수 (RF) 기술은 현대 무선 통신의 핵심 부분으로, 물리적 연결없이 장거리에 걸쳐 데이터 전송을 가능하게합니다.이 기사는 RF의 기본 사항을 탐구하여 전자기 방사선 (EMR)이 RF 커뮤니케이션을 가능하게하는 방법을 설명합니다.우리는 EMR의 원칙, RF 신호의 생성 및 제어 및 광범위한 사용을 탐구 할 것입니다.이 기사는 또한 RF 기술의 역사적 이정표, 관련된 기술 과제 및 안정적인 RF 커뮤니케이션을 보장하는 데 ...1월1일에서 1528

-

CR2450 대 CR2032 : 대신 배터리를 사용할 수 있습니까?

리튬 망간 배터리는 다른 리튬 배터리와 유사합니다.높은 에너지 밀도와 긴 서비스 수명은 공통적 인 특성입니다.이러한 종류의 배터리는 고유 한 안전 때문에 많은 소비자의 신뢰와 호의를 얻었습니다.값 비싼 기술 가제트?우리 집의 작은 가전 제품?주위를 둘러 보면 어디에서나 볼 수 있습니다.이 많은 리튬-망간 배터리 중 CR2450 배터리와 CR2032 배터리는 특히 눈에 띄게됩니다.더 깊은 이해를 위해서는 차이점을 신중하게 ...1월1일에서 1497