# KIOXIA 4Gb, 1.8V Serial Interface NAND Technical Data Sheet

Rev. 2.0 2019 – 10 – 01

**KIOXIA** Corporation

# **CONTENTS**

| 1. | Introduction                                          | 5   |

|----|-------------------------------------------------------|-----|

|    | 1.1. General Description                              |     |

|    | 1.2. Definitions and Abbreviations                    | 5   |

|    | 1.3. Features                                         | 6   |

| 2. | Memory Organization                                   | 7   |

|    | 2.1. Pin Descriptions                                 |     |

|    | 2.2. Pin Assignment (Top View)                        |     |

|    | 2.3. Block Diagram                                    |     |

|    | 2.4. Cell Layout                                      |     |

|    | 2.5. Addressing                                       |     |

|    | 2.6. Valid Blocks                                     |     |

| •  | Physical Interface                                    |     |

| 3. | 3.1. Absolute Maximum Rating                          |     |

|    | 3.2. Capacitance                                      |     |

|    | 3.3. DC Operating Conditions                          |     |

|    | 3.4. Signal Timing                                    |     |

|    | 3.5. AC Characteristics                               |     |

|    | 3.6. DC Operating Characteristics                     |     |

|    | 3.7. Programming, Reading and Erasing Characteristics |     |

|    | 3.8. Power ON/OFF Sequence                            |     |

|    | 3.9. AC Test Condition                                |     |

|    |                                                       |     |

| 4. | Command Description and Device Operation              |     |

|    | 4.1. Command Set                                      |     |

|    | 4.2. Page Read Operation                              | 16  |

|    | 4.2.1. Read Cell Array (13h)                          | 16  |

|    | 4.2.2. Read Buffer (03h or 0Bh)                       |     |

|    | 4.2.3. Read Buffer x2 (3Bh)                           |     |

|    | 4.2.4. Read Buffer x4 (6Bh)                           |     |

|    | ` <i>'</i>                                            |     |

|    | 4.3. Page Read Operation - High Speed Mode            |     |

|    | 4.4. Page Program Operation                           | 20  |

|    | 4.4.1. Program Load (02h)                             | 20  |

|    | 4.4.2. Program Execute (10h)                          |     |

|    | 4.4.3. Program Load Random Data (84h)                 |     |

|    | . ,                                                   |     |

|    | 4.5. Internal Data Move Operation                     |     |

|    | 4.6. Block Erase (D8h)                                |     |

|    | 4.7. Reset (FFh or FEh)                               |     |

|    | 4.8. Write Enable (06h) / Write Disable (04h)         |     |

|    | 4.9. Set Feature (1Fh) / Get Feature (0Fh)            | 26  |

|    | 4.9.1. Set Feature (1Fh)                              | 29  |

|    | 4.9.2. Get Feature (0Fh)                              |     |

|    | 4.10. Block Lock Operation                            | 20  |

|    | 4.11. Block Protection Operation (One Time Program)   |     |

|    | . ,                                                   |     |

|    | 4.11.1. Protect Execute (2Ah)                         |     |

|    | 4.12. Parameter Page Read Operation                   |     |

|    | 4.13. Read ID (9Fh)                                   |     |

|    | 4.14. Unique ID Read Operation                        |     |

|    | 4.15. Bad Block Inhibit                               | 33  |

|    | 4.16. Internal ECC                                    | 34  |

|    | 4.16.1. ECC Switch                                    | 3.4 |

|    | 4.16.2. ECC Status                                    |     |

|    | 4.16.3. ECC Bit Flip Count Detection                  |     |

|    | 4.16.4. ECC Bit Flip Count Report                     |     |

|    | 4.16.5. ECC Maximum Bit Flip Count Report             |     |

# TC58CYG2S0HRAIG

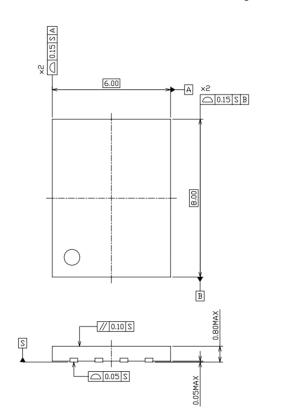

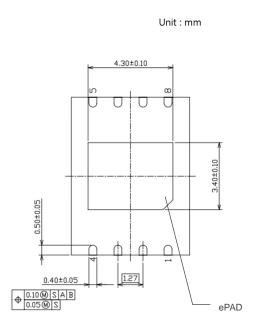

| 5.  | Package Information                                                     | 37 |

|-----|-------------------------------------------------------------------------|----|

|     | 5.1. WSON8 (P-WSON8-0608-1.27-003)                                      | 37 |

| 6.  | Application Notes                                                       | 38 |

|     | 6.1. Prohibition of Unspecified Commands                                | 38 |

|     | 6.2. Restriction of Commands while in the Busy State                    | 38 |

|     | 6.3. Addressing for Page Program Operation                              |    |

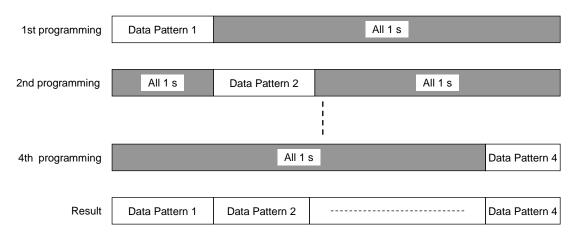

|     | 6.4. Several Programming Cycles on the Same Page (Partial Page Program) | 38 |

|     | 6.5. Power Off Timing                                                   |    |

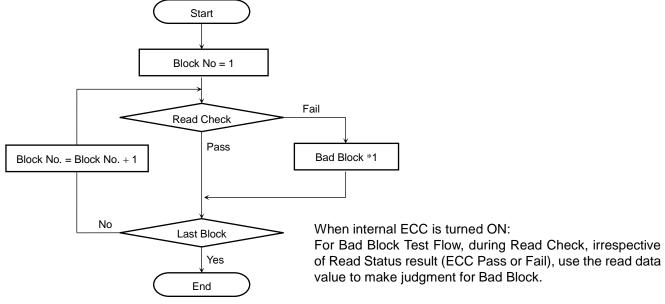

|     | 6.6. Invalid Blocks (Bad Blocks)                                        |    |

|     | 6.7. Failure Phenomena                                                  | 40 |

|     | 6.8 Reliability Guidance                                                | 41 |

|     | 6.9 NAND Management                                                     | 42 |

| 7.  | Revision History                                                        | 43 |

| RFS | TRICTIONS ON PRODUCT USE                                                | 44 |

#### LIST of FIGURES Figure 2. Block Diagram ......8 Figure 3. Cell Layout ......8 Figure 4. Addressing......9 Figure 8. Hold Timing .......12 Figure 9. WP Timing (Example).......12 Figure 10. Power ON/OFF Timing ......14 Figure 12. Page Read from Buffer Timing .......17 Figure 13. Page Read from Buffer x2 Timing .......18 Figure 14. Page Read from Buffer x4 Timing ......19 Figure 16. Program Execute Timing ......21 Figure 19. Reset Timing ......24 Figure 24. Protect Execute Timing .......31 Figure 25. Read ID Timing.......33 LIST of TABLES Table 1 Table 2 Table 3 Capacitance (T<sub>OPR</sub> = 25°C, f = 1MHz).....10 Table 4 Table 5 Table 6 Table 7 Programming, Reading and Erasing Characteristics (T<sub>OPR</sub> = -40 to 85°C, V<sub>CC</sub> = 1.7 to 1.95V).....14 Table 8 Table 9 Table 10 Table 11 Table 12 Table 13 Table 14 Table 15 Table 16 Table 18 Parameter Page .......32 Table 19 Table 20 Page Assignment 34 Table 21 Table 22 Definition of 528 bytes Data Pair ......34 Table 23 Bit Flip Count Detection Status (BFS) (Feature Table - 20h Address Description) .......35 Table 24 Table 25 Table 26 Table 27

#### 1. Introduction

## 1.1. General Description

The TC58CYG2S0HRAIG is a Serial Interface NAND Flash memory for embedded applications which supports the SPI interface. The TC58CYG2S0HRAIG is organized as (4096 + 128) bytes × 64 pages × 2048 blocks. The device has a 4224 byte data buffer which allows program and read data to be transferred between the buffer and the memory cell array in 4224-byte increments. The Erase operation is implemented in a single block unit (256 Kbytes + 8 Kbytes): 4224 bytes × 64 pages). The device has the high speed mode for sequential Page Read operation. When high speed mode is enabled, the average of t<sub>R</sub> is shortened.

The TC58CYG2S0HRAIG has ECC logic on the chip and 8bit read errors for each (512 bytes + 16 bytes) can be corrected. The internal ECC logic has detailed Bit Flip Count Report.

#### 1.2. Definitions and Abbreviations

#### SPI

Serial Peripheral Interface

#### Address

The address is comprised of a column address (CA) with 13 bits and a row address (RA) with 17 bits. The row address identifies the page and block to be accessed. The column address identifies the byte within a page to access.

#### Column

The byte location within the page

#### Row

Refer to the block and page to be accessed

#### Sector

The (512 bytes+16 bytes) unit in a page

## **Page**

The smallest addressable unit for the Read and the Program operations

#### Block

Consists of multiple pages and is the smallest addressable unit for the Erase operation.

#### **Data Buffer**

Buffer used to transfer data to and from the cell array

#### **Cell Array**

Memory cells of NAND Flash

#### **Device**

The packaged NAND unit

#### **ECC**

**Error Correction Code**

#### 1.3. Features

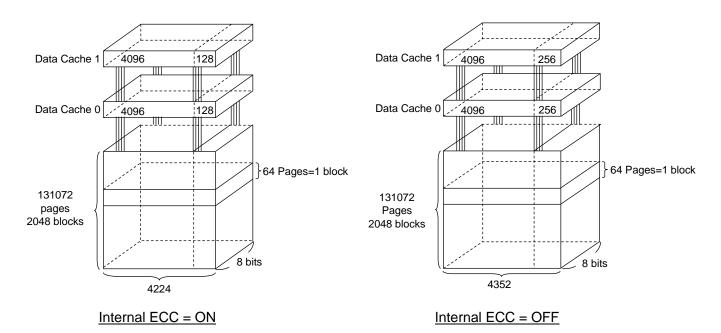

## Organization

Organization (Internal ECC is enabled, default)

Memory Cell Array  $4224 \times 64 \times 2048 \times 8$  bits

Data Buffer 4224 x 8 bits

Page Size 4224 bytes

Block Size (256K + 8K) bytes

Organization (Internal ECC is disabled)

Memory Cell Array 4352 x 64 x 2048 x 8 bits

Data Buffer 4352 x 8 bits

Page Size 4352 bytes

Block Size (256K + 16K) bytes

#### ECC

The device has ECC logic internally. When internal ECC is disabled, 8 bit ECC for each 512 bytes is required.

#### Mode

Page Read, Page Program, Block Erase, Internal Data Move, Reset, Write Enable, Write Disable, Block Lock, Get Feature, Set Feature, Block Protection, Parameter Page Read, Read ID, Unique ID Read

#### Power Supply

$V_{CC} = 1.7 \text{ V to } 1.95 \text{ V}$

#### Access Time

Cell Array to Data Buffer 280  $\mu$ s max 115  $\mu$ s typ. Data Transfer rate 104 MHz max

#### Program/Erase Time

Programming Time 450 μs/page typ. Block Erasing Time 2.7 ms/block typ.

#### Operating Current

Read Operation Current with HSE ON (Average)21 mA maxRead Operation Current with HSE OFF (Average)15 mA maxProgram Operation Current (Average)18 mA maxErase Operation Current (Average)22 mA maxStandby Current180 μA max35 μA typ.

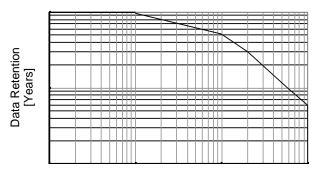

#### Reliability

Refer to reliability note

#### Package

WSON8 (P-WSON8-0608-1.27-003) Weight: 0.12 g typ.

#### Part Numbering Information

TC58CYG2S0HRAIG 4Gb, 1.8V, WSON8 Serial Interface NAND

# 2. Memory Organization

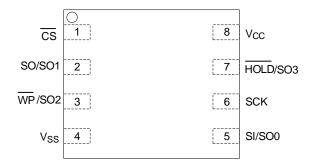

# 2.1. Pin Descriptions

Table 1 Pin Descriptions

| Pin Name | Pin Function                              |

|----------|-------------------------------------------|

| CS       | Chip Select                               |

| SO/SO1   | Serial Data Output / Serial Data Output 1 |

| WP/SO2   | Write Protect / Serial Data Output 2      |

| SI/SO0   | Serial Data Input / Serial Data Output 0  |

| HOLD/SO3 | Hold Input / Serial Data Output 3         |

| SCK      | Serial Clock Input                        |

| Vcc      | Power Supply                              |

| Vss      | Ground                                    |

**Note:** If the WP pin is low and BRWD bit is set to 1, the overwriting for the BRWD (bit [7]) and the BL bits (bits [5:3]) in address A0h of the feature table shown in Table 12 is prohibited.

The users should keep the status of WP signal while CS pin is low.

The HOLD pin and the WP pin are pull up to V<sub>CC</sub> internally.

# 2.2. Pin Assignment (Top View)

Figure 1. WSON8 Pin Assignment

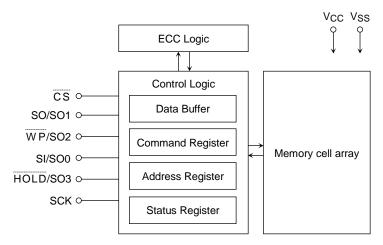

## 2.3. Block Diagram

Figure 2. Block Diagram

#### 2.4. Cell Layout

The Program operation works on page units while the Erase operation works on block units. When internal ECC is turned ON, a page consists of 4224 bytes in which 4096 bytes are used for main memory storage and 128 bytes are used for redundancy or for other uses. In the case that internal ECC is turned OFF, the redundancy area will be expanded to 256 bytes automatically.

Figure 3. Cell Layout

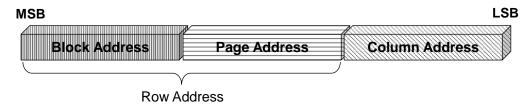

## 2.5. Addressing

There are two address types used; the column address and the row address. The column address is used to access bytes within a page. The row address is used to address pages and blocks. There are some operations that may require only row addresses, such as Block Erase.

Row Address (RA): 17 bits

Block Address (2048 blocks/device) : 11 bits Page Address (64 pages/block) : 6 bits

Column Address (CA): 13 bits

Column Address (4224 or 4352 bytes/page) : 13 bits

Figure 4. Addressing

#### 2.6. Valid Blocks

Table 2 Valid Blocks

| S | Symbol          | Parameter                     | Min  | Тур. | Max  | Unit  |

|---|-----------------|-------------------------------|------|------|------|-------|

|   | N <sub>VB</sub> | Number of Valid (Good) Blocks | 2008 | 1    | 2048 | Block |

Note: The device occasionally contains unusable blocks.

The first block (Block 0) is guaranteed to be a valid block at the time of shipment.

The specification for the minimum number of valid blocks is applicable over the lifetime.

### 3. Physical Interface

# 3.1. Absolute Maximum Rating

Stresses greater than those listed in Table 3 may cause permanent damage to the device. This is a stress rating only.

Table 3 Absolute Maximum Rating

| Symbol              | Parameter                                          | Value                                   | Unit |

|---------------------|----------------------------------------------------|-----------------------------------------|------|

| Vcc                 | Power Supply Voltage                               | -0.3 to 3.9                             | V    |

| VIN                 | Input Voltage                                      | -0.3 to V <sub>CC</sub> + 0.3 (≤ 3.9 V) | V    |

| V <sub>I/O</sub>    | Input /Output Voltage                              | -0.3 to V <sub>CC</sub> + 0.3 (≤ 3.9 V) | V    |

| P <sub>D1</sub>     | Power Dissipation 1                                | 0.42                                    | W    |

| P <sub>D2</sub>     | Power Dissipation 2<br>(WSON8 ePAD without solder) | 0.27                                    | W    |

| T <sub>SOLDER</sub> | Soldering Temperature (10 s)                       | 260                                     | °C   |

| T <sub>STG</sub>    | Storage Temperature                                | -55 to 150                              | °C   |

| T <sub>OPR</sub>    | Operating Temperature                              | -40 to 85                               | °C   |

Note: Avoid locations where the device may be exposed to water (wet, rain, dew condensation, etc.)

## 3.2. Capacitance

Table 4 Capacitance (Topr = 25 °C, f = 1 MHz)

| Symbol | Parameter | Condition  | Min | Max | Unit |

|--------|-----------|------------|-----|-----|------|

| CIN    | Input     | VIN = 0 V  | -   | 2.5 | pF   |

| Соит   | Output    | Vout = 0 V | -   | 4   | pF   |

Note: This parameter is periodically sampled and is not tested for every device.

# 3.3. DC Operating Conditions

Table 5 DC Operating Condition

| able of De Operating Condition |                          |           |      |                       |      |

|--------------------------------|--------------------------|-----------|------|-----------------------|------|

| Symbol                         | Parameter                | Min       | Тур. | Max                   | Unit |

| Vcc                            | Power Supply Voltage     | 1.7       | -    | 1.95                  | V    |

| VIH                            | High Level Input Voltage | Vcc × 0.8 | 1    | Vcc + 0.3             | V    |

| VIL                            | Low Level Input Voltage  | -0.3      | -    | V <sub>CC</sub> × 0.2 | V    |

## 3.4. Signal Timing

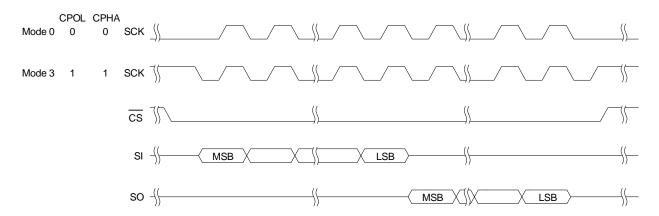

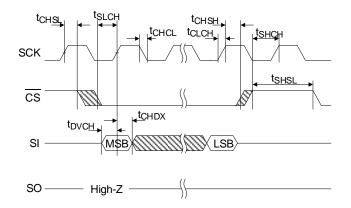

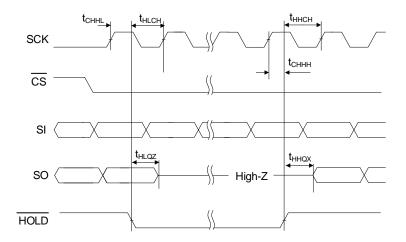

The device supports SPI mode 0 and mode 3. Input data is latched at the rising edge of SCK and data is output at the falling edge of SCK for mode 0 and 3. When HOLD goes Low, the communication is held. The hold state begins at the falling edge of SCK.

Figure 5. SPI Timing

: Don't care

Figure 6. Serial Input Timing

: Don't care

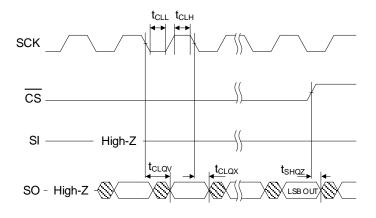

Figure 7. Serial Output Timing

Figure 8. Hold Timing

Figure 9. WP Timing (Example)

## 3.5. AC Characteristics

Table 6 AC Characteristics (Topr = -40 to 85 °C, Vcc = 1.7 to 1.95 V)

| Symbol | Parameter                                 | Min | Тур. | Max                        | Unit |

|--------|-------------------------------------------|-----|------|----------------------------|------|

| Fc     | Serial Clock Frequency for All Operations | -   | -    | 104                        | MHz  |

| tCLH   | Serial Clock High Time                    | 4.5 | -    | -                          | ns   |

| tCLL   | Serial Clock Low Time                     | 4.5 | -    | -                          | ns   |

| tCLCH  | Serial Clock Rise Time (Slew Rate)        | 0.1 | -    | -                          | V/ns |

| tCHCL  | Serial Clock Fall Time (Slew Rate)        | 0.1 | -    | -                          | V/ns |

| tslch  | CS Active Setup Time                      | 4.6 | -    | -                          | ns   |

| tchsh  | CS Active Hold Time                       | 5   | -    | -                          | ns   |

| tshch  | CS Not Active Setup Time                  | 5   | -    | -                          | ns   |

| tCHSL  | CS Not Active Hold Time                   | 5   | -    | -                          | ns   |

| tshsl  | CS High Time                              | 100 | -    | -                          | ns   |

| tshqz  | Output Disable Time                       | -   | -    | 20                         | ns   |

| tCLQX  | Output Hold Time                          | 1   | -    | -                          | ns   |

| tDVCH  | Data In Setup Time                        | 2   | -    | -                          | ns   |

| tCHDX  | Data In Hold Time                         | 5   | -    | -                          | ns   |

| tHLCH  | HOLD Low Setup Time (relative to Clock)   | 5   | -    | -                          | ns   |

| tннсн  | HOLD High Setup Time (relative to Clock)  | 5   | -    | -                          | ns   |

| tCHHL  | HOLD High Hold Time (relative to Clock)   | 5   | -    | -                          | ns   |

| tсннн  | HOLD Low Hold Time (relative to Clock)    | 5   | -    | -                          | ns   |

| tHLQZ  | HOLD Low to High-Z Output                 | -   | -    | 7                          | ns   |

| thhqx  | HOLD High to Output                       | -   | -    | 7                          | ns   |

|        |                                           |     |      | 7.0(C <sub>L</sub> =10 pF) |      |

| tCLQV  | Clock Low to Output Valid                 | -   | -    | 7.5(C <sub>L</sub> =20 pF) | ns   |

|        |                                           |     |      | 8.0(C <sub>L</sub> =30 pF) |      |

| twhsL  | WP Setup Time Before CS Low               | 20  | -    | -                          | ns   |

| tshwl  | WP Hold Time After CS High                | 100 | -    | -                          | ns   |

# 3.6. DC Operating Characteristics

Table 7 DC & Operating Characteristics (Topr = -40 to 85 °C, Vcc = 1.7 to 1.95 V)

| Symbol | Parameter                           | Condition                                                                                     | Min       | Тур. | Max | Unit |

|--------|-------------------------------------|-----------------------------------------------------------------------------------------------|-----------|------|-----|------|

| Iı∟    | Input Leakage Current               | VIN = 0 V to VCC                                                                              | -         | 1    | ±10 | μА   |

| ILO    | Output Leakage Current              | Vout = 0 V to Vcc                                                                             | -         | =    | ±10 | μА   |

| ICCOA1 | Read Operation Current (Average)    | F <sub>C</sub> = 104 MHz<br>High Speed Mode = Enable<br>Read Buffer Command : 03h or 0Bh (x1) | -         | -    | 21  | mA   |

| ICCOA2 | Read Operation Current (Average)    | FC = 104 MHz<br>High Speed Mode = Disable<br>Read Buffer Command : 03h or 0Bh (x1)            | -         | -    | 15  | mA   |

| ІССОАЗ | Program Operation Current (Average) | FC = 104 MHz                                                                                  | -         | -    | 18  | mA   |

| ICCOA4 | Erase Operation Current (Average)   | FC = 104 MHz                                                                                  | -         | -    | 22  | mA   |

| Iccs   | Standby Current                     | CS = V <sub>CC</sub> - 0.2 V, WP = V <sub>CC</sub> , HOLD= V <sub>CC</sub>                    | -         | 35   | 180 | μА   |

| Voн    | High Level Output Voltage           | I <sub>OH</sub> = -0.1 mA                                                                     | Vcc - 0.2 | -    | -   | V    |

| VoL    | Low Level Output Voltage            | I <sub>OL</sub> = 0.1 mA                                                                      | -         | -    | 0.2 | V    |

**Note:** Refer to the High Speed Mode in 4.3. Page Read Operation - High Speed Mode.

I<sub>CCOA1</sub> to I<sub>CCOA4</sub> are the average current during the full operation sequence.

Typ. values reflect values obtained in specific test environments under typical test parameters. Actual results will vary based on the conditions and environment in which the part is used.

## 3.7. Programming, Reading and Erasing Characteristics

Table 8 Programming, Reading and Erasing Characteristics (Tops = -40 to 85 °C, Vcc = 1.7 to 1.95 V)

| SYMBOL             | PARAMETER                                                                                    | MIN | TYP. | MAX | UNIT  |

|--------------------|----------------------------------------------------------------------------------------------|-----|------|-----|-------|

| tPROG              | Programming Time (with ECC)                                                                  | -   | 450  | 600 | μS    |

| N                  | Number of Partial Program Cycles in the Same Page                                            | -   | =    | 4   | times |

| tBERASE            | Block Erasing Time                                                                           | -   | 2.7  | 10  | ms    |

| t <sub>R</sub>     | Cell Array to the Buffer (with ECC) (High Speed Mode = Disable)                              | =   | 115  | 280 | μS    |

| t <sub>RHSA4</sub> | Average Read Time for Sequential Read (with ECC)  (High Speed Mode = Enable, Read Buffer x4) |     | 35   | -   | μS    |

|                    | Device Reset Time (Read)                                                                     | -   | -    | 280 | μS    |

| trst               | Device Reset Time (Program)                                                                  | -   | -    | 600 | μS    |

|                    | Device Reset Time (Erase)                                                                    | -   | =    | 10  | ms    |

**Note:** Refer to the data pair of ECC calculation in 4.16. Internal ECC.

Refer to the High Speed Mode in 4.3. Page Read Operation - High Speed Mode.

t<sub>R</sub> is the average busy time for Page Read operation of 64 pages continuously in a block.

t<sub>RHSA4</sub> is the average busy time for sequential Page Read operation with all data output in each page of 64 pages continuously in a block.

The busy time after Protect Execute command is shorter than t<sub>PROG</sub> (max).

Typ. values reflect values obtained in specific test environments under typical test parameters. Actual results will vary based on the conditions and environment in which the part is used.

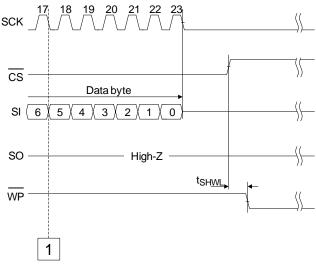

#### 3.8. Power ON/OFF Sequence

The timing sequence shown in the figure below is necessary for the power ON/OFF sequence.

The device internal initialization starts after the power supply reaches an appropriate level in the power on sequence. The users cannot issue any commands while tvsl. From the end of tvsl to the end of tvop, Get Feature and Reset operation can be issued. OIP bit in the feature table indicates the busy state in this time period. All operations are available after tvop.

Figure 10. Power ON/OFF Timing

Table 9 Power on Timing

|                  | g                                      |     |     |       |  |  |  |

|------------------|----------------------------------------|-----|-----|-------|--|--|--|

| Symbol           | Parameter                              | Min | Max | Unit  |  |  |  |

| t <sub>VSL</sub> | Vcc(min) to CS Low                     | -   | 100 | μS    |  |  |  |

| t <sub>VOP</sub> | V <sub>CC</sub> (min) to all operation | -   | 1.1 | ms    |  |  |  |

| tpuw             | Waiting time for power on              | 1   | -   | ms    |  |  |  |

| VCCSR            | Vcc Slew Rate                          | -   | -   | mV/μs |  |  |  |

#### 3.9. AC Test Condition

Table 10 AC Test Condition

| Parameter                      | Condition                                      |

|--------------------------------|------------------------------------------------|

| Falametei                      | Vcc: 1.7 to 1.95 V                             |

| Input level                    | V <sub>CC</sub> × 0.2 to V <sub>CC</sub> × 0.8 |

| Input pulse rise and fall time | 2 ns                                           |

| Input comparison level         | V <sub>CC</sub> / 2                            |

| Output data comparison level   | Vcc/2                                          |

| Output load                    | C <sub>L</sub> (30 pF) + 1 TTL                 |

# 4. Command Description and Device Operation

#### 4.1. Command Set

Table 11 Command Set

| Operation                | Byte 1<br>(CMD) | Byte 2                         | Byte 3                                            | Byte 4                    | Byte 5            | Byte N            |

|--------------------------|-----------------|--------------------------------|---------------------------------------------------|---------------------------|-------------------|-------------------|

| Read Cell Array          | 13h             | Dummy +<br>RA16<br>(Input)     | RA15-RA8<br>(Input)                               | RA7-RA0<br>(Input)        | -                 | -                 |

| Read Buffer              | 03h / 0Bh       | Dummy +<br>CA12-CA8<br>(Input) | CA7-CA0<br>(Input)                                | Dummy                     | D*-D*<br>(Output) | D*-D*<br>(Output) |

| Read Buffer x2           | 3Bh             | Dummy +<br>CA12-CA8<br>(Input) | CA7-CA0                                           | Dummy                     | D*-D*             | D*-D*             |

| Read Buffer x4           | 6Bh             | Dummy +<br>CA12-CA8            | CA7-CA0                                           | Dummy                     | D*-D*             | D*-D*             |

| Program Load             | 02h             | (Input) Dummy + CA12-CA8       | (Input)<br>CA7-CA0                                | D*-D*                     | (Output)<br>D*-D* | (Output) D*-D*    |

| Program Execute          | 10h             | (Input) Dummy + RA16 (Input)   | (Input)  RA15-RA8  (Input)                        | (Input)  RA7-RA0  (Input) | (Input)<br>-      | (Input)<br>-      |

| Protect Execute          | 2Ah             | Dummy +<br>RA16<br>(Input)     | RA15-RA8<br>(Input)                               | RA7-RA0<br>(Input)        | -                 | -                 |

| Program Load Random Data | 84h             | Dummy +<br>CA12-CA8            | CA7-CA0                                           | D*-D*                     | D*-D*             | D*-D*             |

| Block Erase              | D8h             | (Input) Dummy + RA16 (Input)   | (Input) (Input)  RA15-RA8 RA7-RA0 (Input) (Input) |                           | (Input)           | (Input)           |

| Reset                    | FFh / FEh       | -                              | -                                                 | -                         | -                 | -                 |

| Write Enable             | 06h             | -                              | -                                                 | -                         | -                 | -                 |

| Write Disable            | 04h             | -                              | -                                                 | -                         | -                 | -                 |

| Get Feature              | 0Fh             | A7-A0<br>(Input)               | D7-D0<br>(Output)                                 | D7-D0<br>(Output)         | D7-D0<br>(Output) | D7-D0<br>(Output) |

| Set Feature              | 1Fh             | A7-A0<br>(Input)               | D7-D0<br>(Input)                                  | -                         | -                 | -                 |

| Read ID                  | 9Fh             | Dummy                          | ID<br>Byte 0<br>(Output)                          | ID<br>Byte 1<br>(Output)  | Reserved (Output) | Reserved (Output) |

**Note:** 1) Input of a command other than those specified in Table 11 is prohibited. Stored data may be corrupted if an unknown command is entered during the command cycle.

- 2) During the operation in progress, do not input any command except 0Fh, FFh and FEh.

- 3) The users can issue the Protect Execute (2Ah) only one time for each block.

- 4) Once the Get Feature command is issued, the status and setting information are outputted continuously.

## 4.2. Page Read Operation

The Read Cell Array and Read Buffer commands are required to read the data in a page. The Read Cell Array command reads the page data from the NAND cell array to the data buffer. The Read Buffer command reads the data from the data buffer. The operation sequence is as follows.

1. Read Cell Array (13h) : To read the data from

: To read the data from the cell array to the internal data buffer : To read the status (OIP, ECCS0 and ECCS1 bits) of the device

3. Read Buffer (03h or 0Bh) or Read Buffer x2 (3Bh) or Read Buffer x4 (6Bh)

2. Get Feature (0Fh)

: To output the data from the internal data buffer

Read Buffer, Read Buffer x2, Read Buffer x4 and Get Feature commands are repeatable commands. For the Read Buffer x2 and Read Buffer x4 read modes are available as shown in Figure 13 and Figure 14. The users are able to check the detailed bit flip count using ECC Bit Flip Count Detection and other functions using Get Feature command.

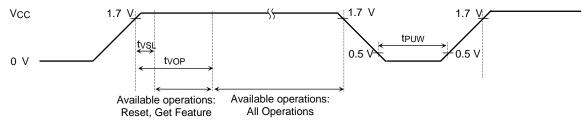

# 4.2.1. Read Cell Array (13h)

Figure 11. Page Read from Cell Array to Buffer

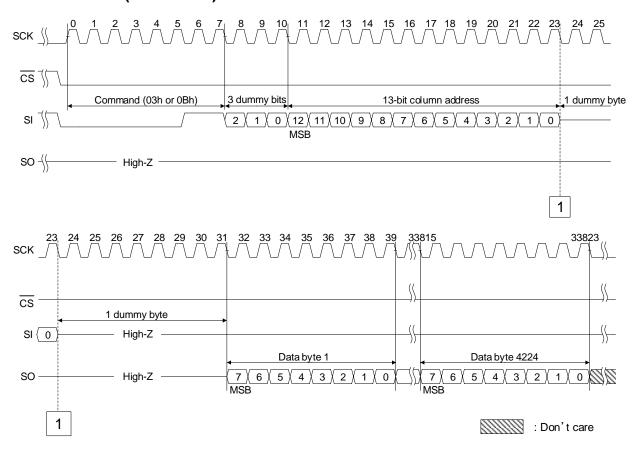

# 4.2.2. Read Buffer (03h or 0Bh)

Note: When internal ECC is turned OFF, the maximum output data size is 4352 Bytes.

Figure 12. Page Read from Buffer Timing

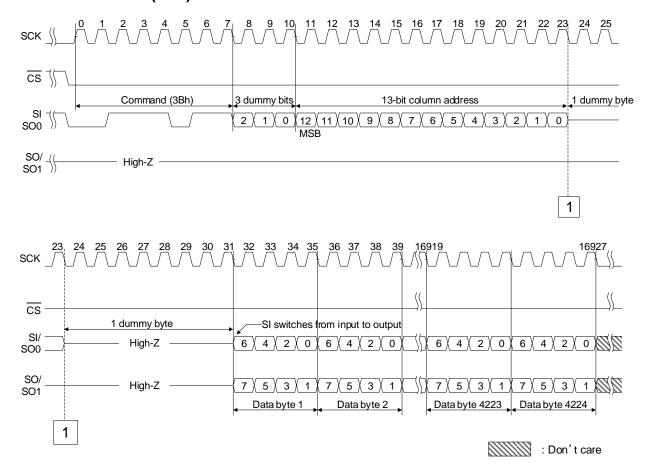

### 4.2.3. Read Buffer x2 (3Bh)

Note: When internal ECC is turned OFF, the maximum output data size is 4352 Bytes.

Figure 13. Page Read from Buffer x2 Timing

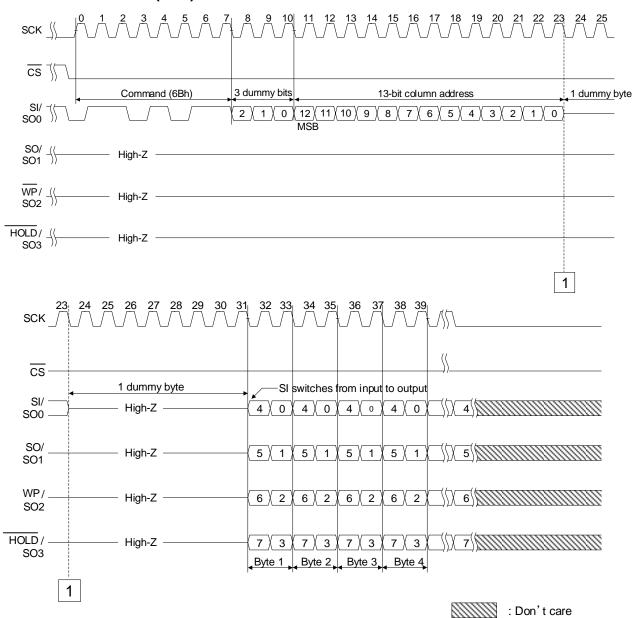

## 4.2.4. Read Buffer x4 (6Bh)

Figure 14. Page Read from Buffer x4 Timing

### 4.3. Page Read Operation - High Speed Mode

The device has a high speed mode for sequential read operation. When high speed mode is enabled, the average  $t_R$  is shortened. The command sequence is the same as the Page Read operation. The users set or clear the HSE bit which enables or disables the high speed mode in the feature table as shown in Table 12. High speed mode is enabled (HSE bit is set to 1) in the default condition. When the users switching the HSE bit, the users have to issue the Set Feature command just before the Read Cell Array (13h) command. When the users use the random page read, the recommended setting of the HSE bit is 0 (disable) since  $t_R$ 0 becomes longer.

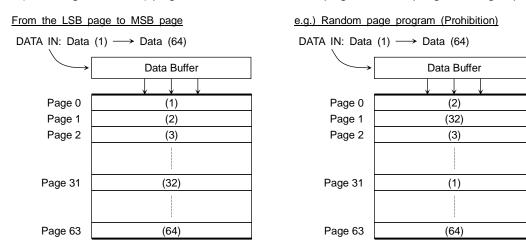

## 4.4. Page Program Operation

The Program Load and Program Execute commands are required to program data to a page. The Program Load command transfers data to the buffer. The unit of data transfer is a byte. The Program Execute command programs data from the buffer to the cell array. The operation sequence is as follows.

1. Write Enable (06h) : To enable the Program operation

2. Program Load (02h)

3. Program Execute (10h)

4. Get Feature (0Fh)

5. To transfer data to the internal data buffer

6. To program data from the buffer to the cell array

6. To read the status (OIP and PRG\_F bits) of the device

The internal data buffer is cleared by the Program Load command.

The Program Load Random Data (84h) command is also available to transfer data to the internal buffer. The users issue Program Load Random Data and the column address before the Program Execute (10h). The operation sequence is as follows.

1. Write Enable (06h) : To enable the Program operation

2. Program Load (02h)

3. Program Load Random Data (84h)

4. Program Execute (10h)

5. Get Feature (0Fh)

To transfer data to the internal data buffer

To program data from the buffer to the cell array

To read the status (OIP and PRG F bits) of the device

Program Load Random Data and Get Feature commands are repeatable command. The internal data buffer is not cleared by the Program Load Random Data command.

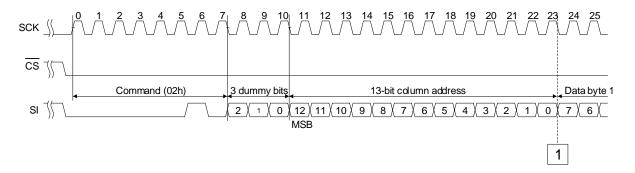

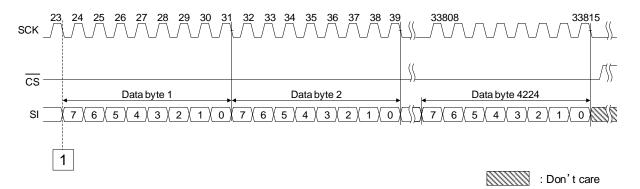

#### 4.4.1. Program Load (02h)

Note: When internal ECC is turned OFF, the maximum input data size is 4352 Bytes.

Figure 15. Program Load

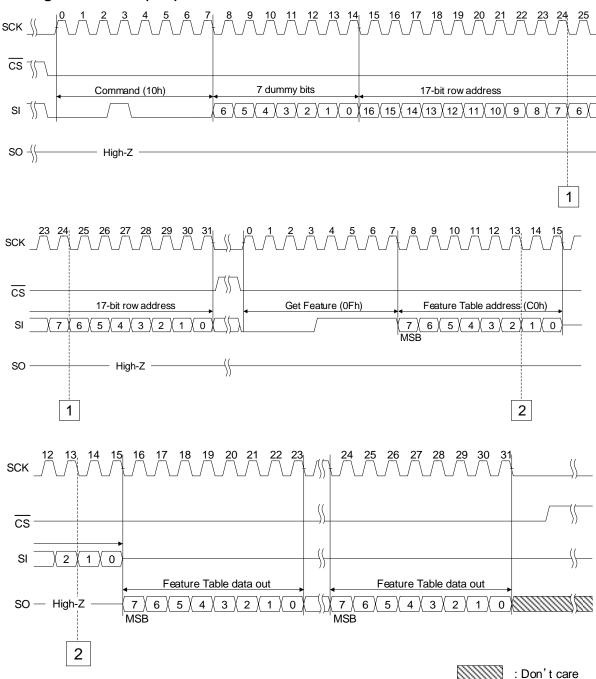

### 4.4.2. Program Execute (10h)

Figure 16. Program Execute Timing

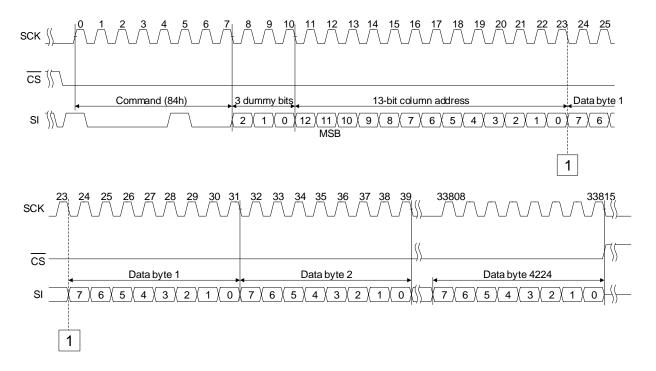

# 4.4.3. Program Load Random Data (84h)

Note: When internal ECC is turned OFF, the maximum input data size is 4352 Bytes.

Figure 17. Program Load Random Data Timing

#### 4.5. Internal Data Move Operation

The Internal Data Move Operation is used to change the data in a page without data output. Before using this operation, the users must disable the Page Read High Speed Mode. The operation sequence is as follows.

1. Set Feature (1Fh) : To disable Page Read High Speed Mode

2. Read Cell Array (13h) : To read data from the cell array to internal buffer

3. Get Feature (0Fh) : To read the status (OIP, ECCS0 and ECCS1 bits) of the device

4. Write Enable (06h) : To enable the write

5. Program Load Random Data (84h) : To change the data in the internal buffer

6. Program Execute (10h) : To program data from the buffer to the cell array 7. Get Feature (0Fh) : To read the status (OIP, PRG\_F bits) of the device

Program Load Random Data and Get Feature commands are repeatable command.

The status of the internal ECC depends on ECC\_E bit in the feature table. When internal ECC is disabled, bit flips are not managed by the device.

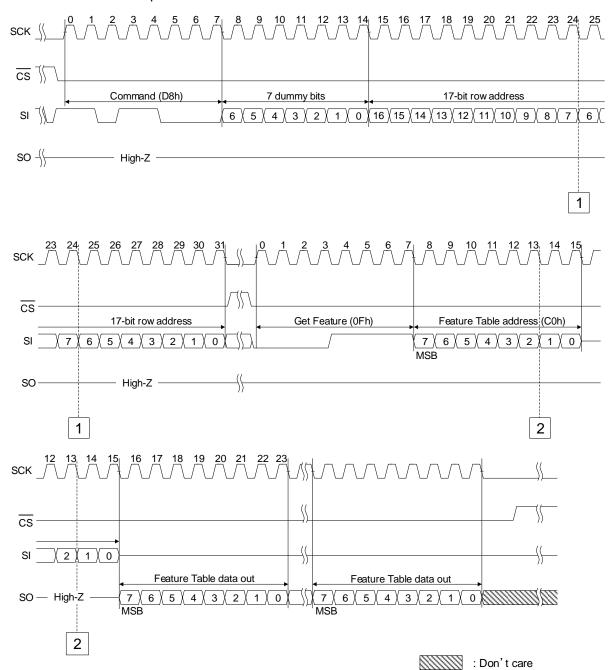

### 4.6. Block Erase (D8h)

The Block Erase operation erases the selected block. The page address is ignored automatically. The operation sequence is as follows.

1. Write Enable (06h) : To enable the Erase operation2. Block Erase (D8h) : To erase data in the block

3. Get Feature (0Fh) : To read the status (OIP and ERS\_F bits) of the device

Get Feature command is repeatable command.

Figure 18. Block Erase Timing

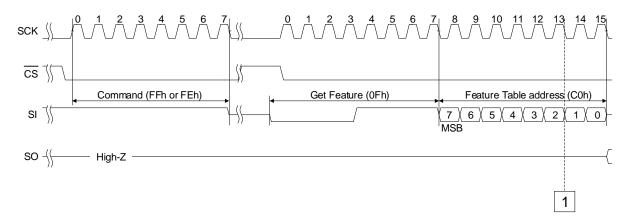

## 4.7. Reset (FFh or FEh)

The device offers Reset operation by command FFh or FEh. For example, in case of a Program or Erase operation, the internally generated voltage is discharged and the device enters the busy state. The operation sequence is as follows.

1. Reset (FFh or FEh) : To reset the device

2. Get Feature (0Fh) : To read the status of the device

Get Feature command is repeatable command.

Figure 19. Reset Timing

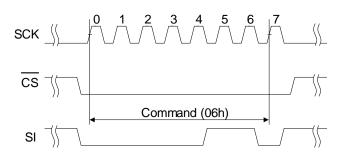

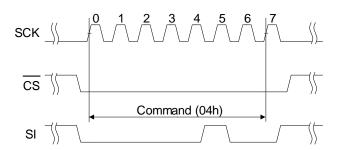

# 4.8. Write Enable (06h) / Write Disable (04h)

The Write Enable/Disable commands set or reset the WEL (Write Enable Latch) bit in the feature table shown in Table 12. The Write Enable command sets the WEL bit to 1. The Write Enable command must be issued before the Page Program, Block Protection and Block Erase operations. The Write Disable command clears the WEL bit to 0. If the WEL bit is cleared, Page Program, Block Protection and Block Erase commands are ignored by the device.

Figure 20. Write Enable Timing

Figure 21. Write Disable Timing

## 4.9. Set Feature (1Fh) / Get Feature (0Fh)

The users set individual features using the Set Feature operation and get feature settings or status of the device using the Get Feature operation. Feature settings and status are shown in Table 12. Refer to other sections for the details of each setting and status. When a feature is set once by the Set Feature command, the device keeps the bit until power OFF even if a Reset (FFh or FEh) command is issued.

Table 12 Feature Table

| Address |                |                |               | В              | it           |              |              |              |  |

|---------|----------------|----------------|---------------|----------------|--------------|--------------|--------------|--------------|--|

| Address | 7              | 6              | 5             | 4              | 3            | 2            | 1            | 0            |  |

| A0h     | BRWD<br>(R/W)  | Reserved       | BL2<br>(R/W)  | BL1<br>(R/W)   | BL0<br>(R/W) | Reserved     | Reserved     | Reserved     |  |

| B0h     | PRT_E<br>(R/W) | IDR_E<br>(R/W) | Reserved      | ECC_E<br>(R/W) | Reserved     | BBI<br>(R)   | HSE<br>(R/W) | Reserved     |  |

| C0h     | Reserved       | Reserved       | ECCS1<br>(R)  | ECCS0<br>(R)   | PRG_F<br>(R) | ERS_F<br>(R) | WEL<br>(R/W) | OIP<br>(R)   |  |

| 10h     | BFD3<br>(R/W)  | BFD2<br>(R/W)  | BFD1<br>(R/W) | BFD0<br>(R/W)  | Reserved     | Reserved     | Reserved     | Reserved     |  |

| 20h     | BFS7<br>(R)    | BFS6<br>(R)    |               |                | BFS3<br>(R)  | BFS2<br>(R)  | BFS1<br>(R)  | BFS0<br>(R)  |  |

| 30h     | MBF3<br>(R)    | MBF2<br>(R)    | MBF1<br>(R)   | MBF0<br>(R)    | Reserved     | MFS2<br>(R)  | MFS1<br>(R)  | MFS0<br>(R)  |  |

| 40h     | BFR7<br>(R)    | BFR6<br>(R)    | BFR5<br>(R)   | BFR4<br>(R)    | BFR3<br>(R)  | BFR2<br>(R)  | BFR1<br>(R)  | BFR0<br>(R)  |  |

| 50h     | BFR15<br>(R)   | BFR14<br>(R)   | BFR13<br>(R)  | BFR12<br>(R)   | BFR11<br>(R) | BFR10<br>(R) | BFR9<br>(R)  | BFR8<br>(R)  |  |

| 60h     | BFR23<br>(R)   |                |               | BFR20<br>(R)   | BFR19<br>(R) | BFR18<br>(R) | BFR17<br>(R) | BFR16<br>(R) |  |

| 70h     | _              |                |               | BFR28<br>(R)   | BFR27<br>(R) | BFR26<br>(R) | BFR25<br>(R) | BFR24<br>(R) |  |

Note: (R/W): Read / Write, (R): Read only

The users must use the Write Enable (06h) or the Write Disable (04h) command to switch the WEL bit since Set Feature command cannot change it.

The value of Reserved bits in Feature Table is 0.

The access to any unknown address which is not defined in this Feature Table is not allowed.

The bits in Feature Table which are related to ECC functions become valid when the Internal ECC is turned on by the setting of ECC\_E bit (bit [4]) in address B0h.

All the bits in Feature Table will be back to the default value after the power on sequence.

Table 13 Feature Table - A0h Address Description

| Bit | Symbol   | Parameter                       | Read<br>/ Write | Description                                                                                                                              |

|-----|----------|---------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | BRWD     | Block Register<br>Write Disable | R/W             | When WP pin is Low and BRWD is set to 1, over write for BRWD and BL bits are prohibit.  1b: Disable  0b: Enable (Default)                |

| 6   | Reserved | -                               | ı               | Reserved                                                                                                                                 |

| 5   | BL2      | Block Lock 2                    | R/W             | The users set the locked blocks as entire of device or portion of device using the BL bits.  000b: All Unlocked  001b: Upper 1/64 Locked |

| 4   | BL1      | Block Lock 1                    | R/W             | 010b: Upper 1/32 Locked<br>011b: Upper 1/16 Locked                                                                                       |

| 3   | BL0      | Block Lock 0                    | R/W             | 100b: Upper 1/8 Locked 101b: Upper 1/4 Locked 110b: Upper 1/2 Locked 111b: All Locked (Default)                                          |

| 2   | Reserved | -                               | =               | Reserved                                                                                                                                 |

| 1   | Reserved | -                               | -               | Reserved                                                                                                                                 |

| 0   | Reserved | -                               | =               | Reserved                                                                                                                                 |

Note: (R/W): Read / Write, (R): Read only

Refer to the description of BRWD and BL2-0 in 4.10. Block Lock Operation.

Table 14 Feature Table - B0h Address Description

| Bit | Symbol   | Parameter              | Read<br>/ Write | Description                                                                                                                                                            |

|-----|----------|------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PRT_E    | Block Protect Enable   | R/W             | The setting for Block Protection.  0b: Normal Operation (Default)  1b: Block Protection Enable – The Protect Execute command (2Ah) is acceptable for block protection. |

| 6   | IDR _E   | ID Read Enable         | R/W             | The setting for Parameter Page Read and Unique ID Read. 0b: Normal Operation (Default) 1b: Parameter Page Read and Unique ID read mode                                 |

| 5   | Reserved | -                      | =               | Reserved                                                                                                                                                               |

| 4   | ECC _E   | ECC Enable             | R/W             | The setting for internal ECC Function.  0b: Internal ECC Disable  1b: Internal ECC Enable (Default)                                                                    |

| 3   | Reserved | -                      | -               | Reserved                                                                                                                                                               |

| 2   | BBI      | Bad Block Inhibit      | R               | The setting for Bad Block Inhibit Function.  0b: Not Available  1b: Bad Block Inhibit Enable (Default)                                                                 |

| 1   | HSE      | High Speed Mode Enable | R/W             | The setting for Page Read High Speed Mode.  Ob: High Speed Mode Disable  1b: High Speed Mode Enable (Default)                                                          |

| 0   | Reserved | -                      | i               | Reserved                                                                                                                                                               |

Note: (R/W): Read / Write, (R): Read only

Refer to the description of PRT\_E in 4.11. Block Protection Operation (One Time Program).

Refer to the description of ECC\_E in 4.16.1 ECC Switch.

Refer to the description of BBI in 4.15. Bad Block Inhibit.

Refer to the description of HSE in 4.3. Page Read Operation - High Speed Mode.

Table 15 Feature Table - C0h Address Description

| Bit                                                               | Symbol   | Parameter                                                                                                                                                                      | Read<br>/ Write | Description                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                                                                 | Reserved | -                                                                                                                                                                              | 1               | Reserved                                                                                                                                                                                                                                                                                                                                       |

| 6                                                                 | Reserved | -                                                                                                                                                                              | ı               | Reserved                                                                                                                                                                                                                                                                                                                                       |

| 5                                                                 | ECCS1    | ECC Status 1                                                                                                                                                                   | R               | ECC status bits indicate the status of internal ECC operation.  00b: No bit flips were detected in previous page read.  01b: Bit flips were detected and corrected.  Bit flip count was less than the threshold bit count.                                                                                                                     |

| 4                                                                 | ECCS0    | ECC Status 0                                                                                                                                                                   | R               | The threshold bit count is set by bits [7:4] in address 10h in the feature table.  10b: Multiple bit flips were detected and not corrected.  11b: Bit flips were detected and corrected.  Bit flip count was equal to or more than the threshold bit count.  The threshold bit count is set by bits [7:4] in address 10h in the feature table. |

| 3                                                                 | PRG_F    | Program Fail                                                                                                                                                                   | R               | Program fail bit indicates that a program failure has occurred in the previous Program Operation or Block Protection operation.  0b: Program Pass  1b: Program Fail                                                                                                                                                                            |

| 2                                                                 | ERS_F    | Erase Fail                                                                                                                                                                     | R               | Erase fail bit indicates that an erase failure has occurred in the previous Erase operation.  0b: Erase Pass 1b: Erase Fail                                                                                                                                                                                                                    |

| 1                                                                 | WEL      | Write Enable Latch                                                                                                                                                             | R/W             | This bit indicates the status of write enable/disable.  Ob: Write Disable (Default)  1b: Write Enable                                                                                                                                                                                                                                          |

| 0 OIP Operation In Progress R 0b: Operation is not in progress. F |          | This bit indicates the status of the device. This bit will be set while busy state.  0b: Operation is not in progress. Ready state.  1b: Operation is in progress. Busy state. |                 |                                                                                                                                                                                                                                                                                                                                                |

Note: (R/W): Read / Write, (R): Read only

The users must use the Write Enable (06h) or the Write Disable (04h) command to switch the WEL bit since Set Feature command cannot change it.

Once the Get Feature command is issued, the status and setting information are outputted continuously.

OIP, PRG\_F, ERS\_F bits are updated automatically during the status information are outputted continuously.

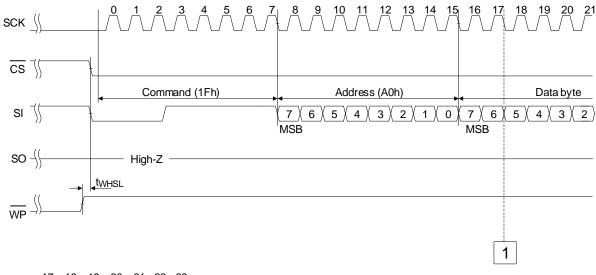

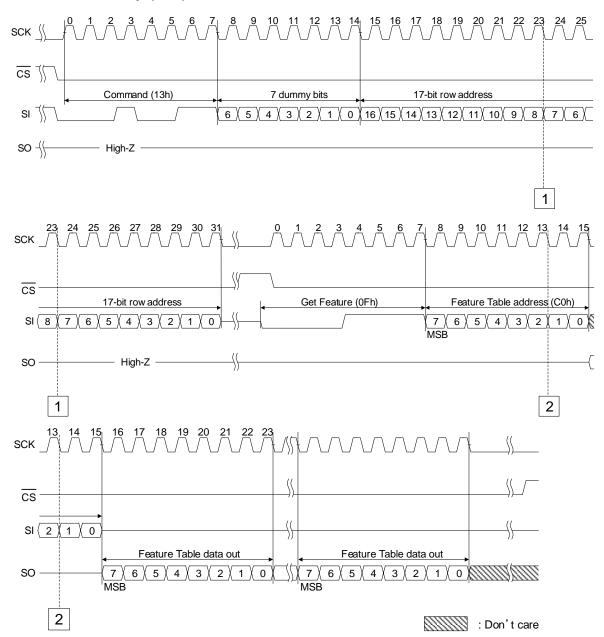

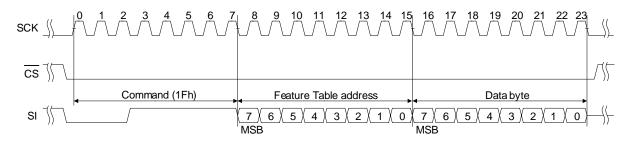

## **4.9.1. Set Feature (1Fh)**

Figure 22. Set Feature Timing

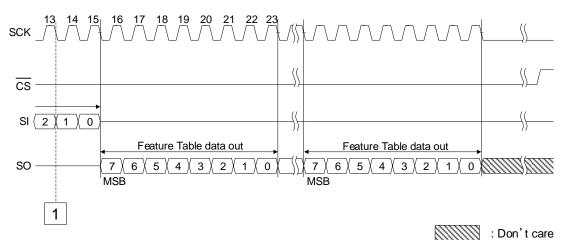

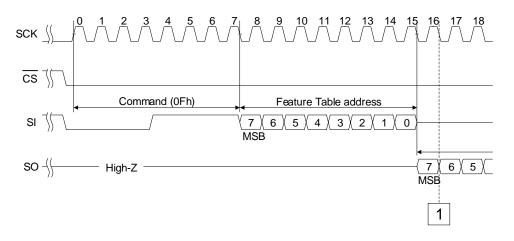

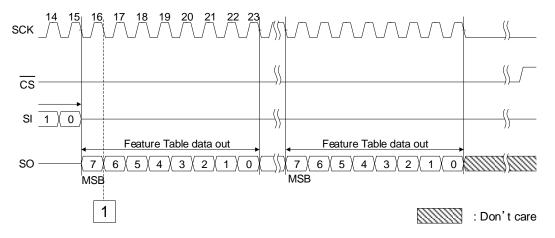

# 4.9.2. Get Feature (0Fh)

After the Get Feature command and the address are input, the 8 bit status and setting information will be output continuously until  $\overline{CS}$  goes High.

Figure 23. Get Feature Timing

© 2016-2019 KIOXIA Corporation 29 2019-10-01

#### 4.10. Block Lock Operation

The Block Lock Operation prevents Page Program, Block Protection and Block Erase operations. The users set the range of locked blocks as the entire device or a portion of the device using the BL bits (bits [5:3]) in address A0h of the feature table shown in Table 12. The users set the BL bits by the Set Feature operation. After the power on sequence, all blocks are locked (bits [5:3] are all set to 1). If the Program Execute (10h), Protect Execute (2Ah) or Block Erase (D8h) command is issued to locked blocks, Program Fail or Erase Fail will be indicated in the feature table shown in Table 12.

The users must clear / change the BL bits using Set Feature command to unlock the entire of the device or portion of the device. When BRWD bit is set and WP pin is Low, the users cannot switch the BRWD and the BL bits.

The Block Lock Operation is different from the Block Protection Operation.

Table 16 Block Lock Setting

| BL2 | BL1 | BL0 | Protected Area    | Protected Blocks   |  |  |  |  |

|-----|-----|-----|-------------------|--------------------|--|--|--|--|

| 0   | 0   | 0   | All Unlocked      | None               |  |  |  |  |

| 0   | 0   | 1   | Upper 1/64 Locked | Block 2016 to 2047 |  |  |  |  |

| 0   | 1   | 0   | Upper 1/32 Locked | Block 1984 to 2047 |  |  |  |  |

| 0   | 1   | 1   | Upper 1/16 Locked | Block 1920 to 2047 |  |  |  |  |

| 1   | 0   | 0   | Upper 1/8 Locked  | Block 1792 to 2047 |  |  |  |  |

| 1   | 0   | 1   | Upper 1/4 Locked  | Block 1536 to 2047 |  |  |  |  |

| 1   | 1   | 0   | Upper 1/2 Locked  | Block 1024 to 2047 |  |  |  |  |

| 1   | 1   | 1   | All Locked        | Block 0 to 2047    |  |  |  |  |

#### 4.11. Block Protection Operation (One Time Program)

The Block Protection Operation provides the function to prohibit the Program and Erase operations to user selected blocks. The users protect individual blocks using the Set Feature, Write Enable and Protect Execute commands. The last 128 blocks of the device are able to be set to protected blocks. The block protection setting is permanent. Once a block is protected, the users cannot unprotect the block.

When PRT\_E (bit [7]) in address B0h of the feature table is set to 1, and the users issue the Protect Execute command (2Ah), the user block will become a protected block. The users must set the PRT\_E bit (bit [7]) just before the Write Enable command for the Protect Execute. After the protection to the block, the users must clear bit [7] in address B0h using the Set Feature command. The users can issue the Protect Execute (2Ah) only one time for each block.

The Block Protection Operation is different from the Block Lock Operation.

The operation sequence to set block "N" as a protected block is as follows.

1. Set Feature (1Fh) : To set PRT\_E bit [7] in address B0h to block protection mode

2. Write Enable (06h) : To enable the Protect Execute command

3. Protect Execute (2Ah) for block "N" : To protect the block "N"

4. Get Feature (0Fh) : To read the status (OIP and PRG F bits) of the device

5. Set Feature (1Fh) : To clear PRT\_E bit [7] in address B0h

Get Feature command is repeatable command.

Table 17 Block Protection Setting

| PRT_E | State                                                                                           |

|-------|-------------------------------------------------------------------------------------------------|

| 0     | Normal Operation (Default)                                                                      |

| 1     | Block Protection Enable – The Protect Execute command (2Ah) is acceptable for Block Protection. |

Table 18 Block Number for Block Protection

| Block Number            | Block Protection                                                     |  |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|

| Block 0 – Block 1919    | The users cannot protect these blocks by Block Protection operation. |  |  |  |  |  |  |

| Block 1920 – Block 2047 | The users can protect these blocks by Block Protection operation.    |  |  |  |  |  |  |

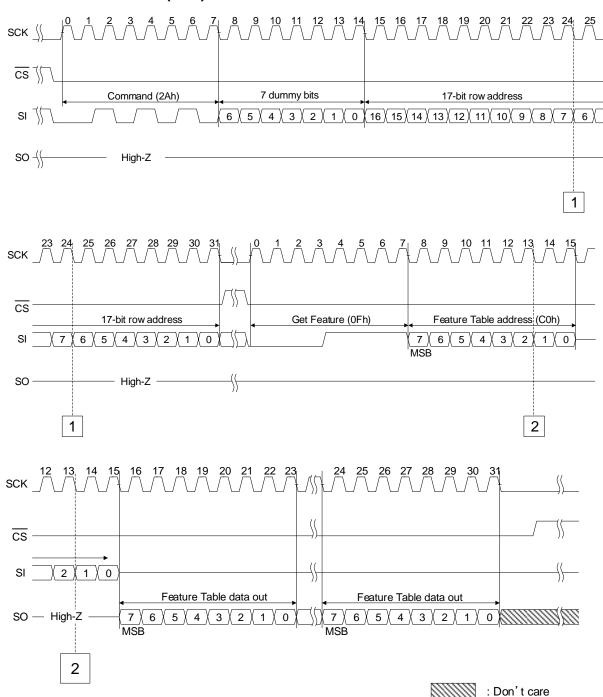

# 4.11.1. Protect Execute (2Ah)

Figure 24. Protect Execute Timing

© 2016-2019 KIOXIA Corporation 31 2019-10-01

#### 4.12. Parameter Page Read Operation

The device has a parameter page. The operation sequence is as follows.

1. Set Feature (1Fh) with address B0h and set bit [6] : To set the IDR\_E bit in the feature table

2. Read Cell Array (13h) with address 01h : To read the parameter page

3. Get Feature (0Fh) : To read the status (OIP bit) of the device

4. Read Buffer (03h or 0Bh) with address 00h : To output the parameter page

or Read Buffer x2 (3Bh) or Read Buffer x4 (6Bh)

5. Set Feature (1Fh) with address B0h and clear bit [6] : To clear the IDR\_E bit in the feature table

Read Buffer, Read Buffer x2, Read Buffer x4 and Get Feature commands are repeatable commands.

Table 19 Parameter Page

| Byte      | Parameter                                      | Value                                                                                              |

|-----------|------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 0 - 3     | Signature                                      | 4Eh, 41h, 4Eh, 44h                                                                                 |

| 4 - 31    | Reserved                                       | All 00h                                                                                            |

| 32 - 43   | Device manufacturer                            | 54h, 4Fh, 53h, 48h, 49h, 42h, 41h, 20h, 20h, 20h, 20h                                              |

| 44 - 63   | Device model; TC58CYG2S0HRAIG                  | 54h, 43h, 35h, 38h, 43h, 59h, 47h, 32h, 53h, 30h, 48h, 52h, 41h, 49h, 47h, 20h, 20h, 20h, 20h, 20h |

| 64        | Manufacturer ID                                | 98h                                                                                                |

| 65 - 79   | Reserved                                       | All 00h                                                                                            |

| 80 - 83   | Number of data bytes per page                  | 00h, 10h, 00h, 00h                                                                                 |

| 84 - 85   | Number of spare bytes per page                 | 80h, 00h                                                                                           |

| 86 - 89   | Number of data bytes per partial page          | 00h, 02h, 00h, 00h                                                                                 |

| 90 - 91   | Number of spare bytes per partial page         | 10h, 00h                                                                                           |

| 92 - 95   | Number of pages per block                      | 40h, 00h, 00h, 00h                                                                                 |

| 96 - 99   | Number of blocks per unit                      | 00h, 08h, 00h, 00h                                                                                 |

| 100       | Number of logical units                        | 01h                                                                                                |

| 101       | Reserved                                       | 00h                                                                                                |

| 102       | Number of bits per cell                        | 01h                                                                                                |

| 103 - 104 | Bad blocks maximum per unit                    | 28h, 00h                                                                                           |

| 105 - 106 | Block endurance                                | 01h, 05h                                                                                           |

| 107       | Guaranteed valid blocks at beginning of target | 01h                                                                                                |

| 108 - 109 | Reserved                                       | All 00h                                                                                            |

| 110       | Number of programs per page                    | 04h                                                                                                |

| 111       | Reserved                                       | 00h                                                                                                |

| 112       | Number of ECC bits                             | 00h                                                                                                |

| 113 - 127 | Reserved                                       | All 00h                                                                                            |

| 128       | I/O pin capacitance                            | 04h                                                                                                |

| 129 - 132 | Reserved                                       | All 00h                                                                                            |

| 133 - 134 | tpROG maximum page program time                | 58h, 02h                                                                                           |

| 135 - 136 | tBERASE maximum block erase time               | 10h, 27h                                                                                           |

| 137 - 138 | t <sub>R</sub> maximum page read time          | 18h, 01h                                                                                           |

| 139 - 253 | Reserved                                       | All 00h                                                                                            |

| 254 - 255 | Integrity CRC                                  | 9Bh, 4Ah                                                                                           |

| 256 - 511 | Value of bytes 0–255                           | -                                                                                                  |

| 512 - 767 | Value of bytes 0–255                           | -                                                                                                  |

**Note:** The value of all parameters are default setting of the device.

When the users change the setting of the device such as internal ECC enable/disable, parameter page is not updated.

The Integrity CRC (Cyclic Redundancy Check) field is used to verify that the contents of the Parameter Page were transferred correctly to the host. The CRC of the Parameter Page is a word (16-bit) field. The CRC calculation covers all of data between byte 0 and byte 253 of the Parameter Page inclusive.

The CRC shall be calculated on byte (8-bit) quantities starting with byte 0 in the Parameter Page. The bits in the 8-bit quantity are processed from the most significant bit (bit 7) to the least significant bit (bit 0).

The CRC shall be calculated using the following 16-bit generator polynomial:

$G(X) = X_{16} + X_{15} + X_2 + 1$

This polynomial in hex may be represented as 8005h.

The CRC value shall be initialized with a value of 4F4Eh before the calculation begins. There is no XOR applied to the final CRC value after it is calculated. There is no reversal of the data bytes or the CRC calculated value.

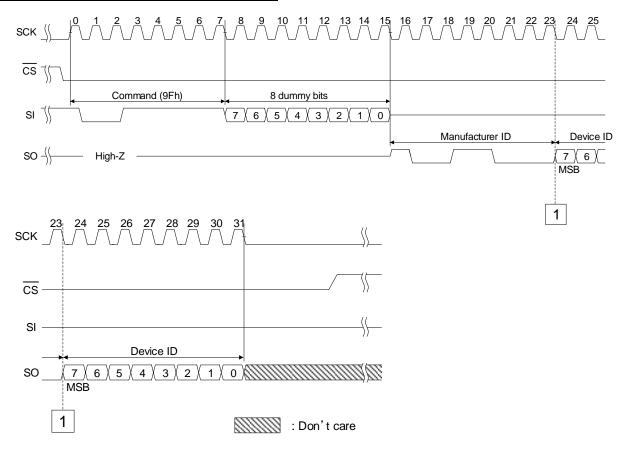

#### 4.13. Read ID (9Fh)

The ID of the device is read by command 9Fh.

Table 20 ID Table

| Byte   | Description             | Value |

|--------|-------------------------|-------|

| Byte 0 | Manufacture ID (KIOXIA) | 98h   |

| Byte 1 | Device ID               | BDh   |

Figure 25. Read ID Timing

#### 4.14. Unique ID Read Operation

The device has a unique ID and it is different for each device. The device has 16 copies of 32 bytes of unique ID data. The first 16 bytes of data are unique ID data and the second 16 bytes of data are the complement value of the first 16 bytes of data. The operation sequence is as follows.

1. Set Feature (1Fh) with address B0h and set bit [6] : To set the IDR\_E bit in the feature table

2. Read Cell Array (13h) with address 00h : To read the unique ID

3. Get Feature (0Fh) : To read the status (OIP bit) of the device

4. Read Buffer (03h or 0Bh) with address 00h : To output the 16 copies of the Unique ID

or Read Buffer x2 (3Bh) or Read Buffer x4 (6Bh)

5. Set Feature (1Fh) with address B0h and clear bit [6] : To clear the IDR\_E bit in the feature table

Read Buffer, Read Buffer x2, Read Buffer x4 and Get Feature commands are repeatable commands.

#### 4.15. Bad Block Inhibit

The device occasionally contains unusable blocks in its initial condition. The Page Program, Block Protection and Erase operation are prohibited to invalid blocks. The device has a Bad Block Inhibit function to protect initial invalid blocks. When the users issue the Program or Erase command to the initial invalid blocks, the device ignores these commands automatically and program fail or erase fail is indicated in the feature table as shown in Table 12. The Bad Block Inhibit function is enabled by default and this setting is permanent.

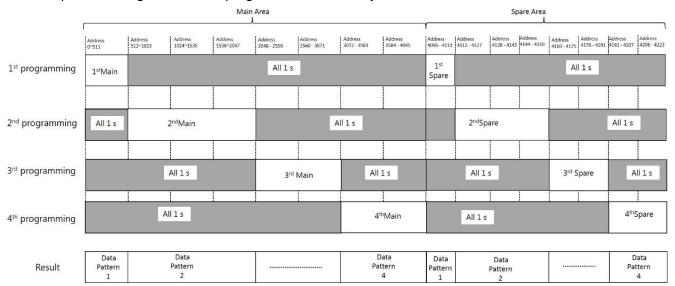

#### 4.16. Internal ECC

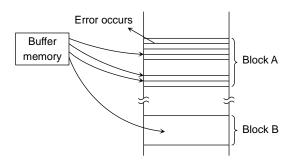

The device has internal ECC and it generates error correction code during the busy time in a Program operation. The ECC logic manages 9bit error detection and 8bit error correction in each 528 bytes of main and spare data. A section of the main area (512 bytes) and spare area (16 bytes) are paired for ECC calculation. During the Read operation, the device executes ECC by itself. Once the Read command is executed, the Get Feature command can be issued to check the read status. The read status remains until other valid commands are executed.

The device has the functions of Bit Flip Detection and Maximum Bit Flip Count Report. Internal ECC detects the bit flips in each sector and the maximum bit flip count in a page. These results are indicated in the feature table as shown in Table 12.

Table 21 Page Assignment

| 1st<br>Main | 2nd<br>Main | 3rd<br>Main |      | 5th<br>Main |      |      | 8th<br>Main | 1st<br>Spare | 2nd<br>Spare | 3rd<br>Spare | 4th<br>Spare |     |     | 7   | 8th<br>Spare | Internal ECC Parity Area |

|-------------|-------------|-------------|------|-------------|------|------|-------------|--------------|--------------|--------------|--------------|-----|-----|-----|--------------|--------------------------|

| 512B        | 512B        | 512B        | 512B | 512B        | 512B | 512B | 512B        | 16B          | 16B          | 16B          | 16B          | 16B | 16B | 16B | 16B          | 128B                     |

Table 22 Definition of 528 bytes Data Pair

| <u> </u>                 |                |              |  |  |  |  |  |

|--------------------------|----------------|--------------|--|--|--|--|--|

| Data Pair                | Column Address |              |  |  |  |  |  |

| Dala Fall                | Main Area      | Spare Area   |  |  |  |  |  |

| 1st Data Pair (Sector 0) | 0 to 511       | 4096 to 4111 |  |  |  |  |  |

| 2nd Data Pair (Sector 1) | 512 to 1023    | 4112 to 4127 |  |  |  |  |  |

| 3rd Data Pair (Sector 2) | 1024 to 1535   | 4128 to 4143 |  |  |  |  |  |

| 4th Data Pair (Sector 3) | 1536 to 2047   | 4144 to 4159 |  |  |  |  |  |

| 5th Data Pair (Sector 4) | 2048 to 2559   | 4160 to 4175 |  |  |  |  |  |

| 6th Data Pair (Sector 5) | 2560 to 3071   | 4176 to 4191 |  |  |  |  |  |

| 7th Data Pair (Sector 6) | 3072 to 3583   | 4192 to 4207 |  |  |  |  |  |

| 8th Data Pair (Sector 7) | 3584 to 4095   | 4208 to 4223 |  |  |  |  |  |

**Note:** The ECC parity code generated by internal ECC is stored in column addresses 4224-4351 and the users cannot access to these specific addresses when internal ECC is enabled. While using the Partial Page Program, the users must program the data to main area and spare area simultaneously by the definition of data pair.

#### 4.16.1. ECC Switch

The internal ECC is enabled after the power on sequence. The users set or clear the ECC\_E bit (bit [4]) in address B0h of the feature table to enable or disable the internal ECC by the Set Feature command. If the ECC\_E bit is cleared to 0 in the feature table, internal ECC will be disabled. In this case, the spare area size is changed from 128 bytes to 256 bytes automatically. When the users switching the ECC\_E bit, the users must issue the Set Feature command just before the Page Read, Page Program or Block Erase operation.

#### 4.16.2. ECC Status

The ECC Status function is used to monitor the error correction status. The device can correct up to 8bit errors. ECC is performed on the NAND Flash main and spare areas. The ECC status is indicated in the ECCS1 and ECCS0 bit (bits [5:4]) in address C0h of the feature table shown in Table 15. The users issue the Get Feature command to read the ECC status.

#### 4.16.3. ECC Bit Flip Count Detection

The ECC Bit Flip Count Detection function detects the bit flip count in a page. The users set the threshold bit count using the Set Feature command. The threshold bit count is decided by BFD bit in address 10h in the feature table as shown in Table 12. The detected results will be indicated in the BFS bits (bits [7:0]) in address 20h. When bit flips exceed the threshold in a sector, the BFS bits are set after the Read Buffer command.

Table 23 Bit Flip Count Detection Setting (BFD)

| BFD3 | BFD2 | BFD1 | BFD0 | Description                                                |

|------|------|------|------|------------------------------------------------------------|

| 0    | 0    | 0    | 0    | Reserved                                                   |

| 0    | 0    | 0    | 1    | Detect 1 bit flip in a sector                              |

| 0    | 0    | 1    | 0    | Detect 2 bit flips in a sector                             |

| 0    | 0    | 1    | 1    | Detect 3 bit flips in a sector                             |

| 0    | 1    | 0    | 0    | Detect 4 bit flips in a sector (Default)                   |

| 0    | 1    | 0    | 1    | Detect 5 bit flips in a sector                             |

| 0    | 1    | 1    | 0    | Detect 6 bit flips in a sector                             |

| 0    | 1    | 1    | 1    | Detect 7 bit flips in a sector                             |

| 1    | 0    | 0    | 0    | Detect 8 bit flips in a sector                             |

| 1    | 1    | 1    | 1    | Detect the uncorrectable error (9+ bit errors in a sector) |

Table 24 Bit Flip Count Detection Status (BFS) (Feature Table - 20h Address Description)

| Iabic | ble 24 Bit Filp Count Detection Status |                                   |                 | eature rable - zon Address Description)                                                                                                                                                                                                                         |

|-------|----------------------------------------|-----------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Symbol                                 | Parameter                         | Read<br>/ Write | Description                                                                                                                                                                                                                                                     |

| 7     | BFS7                                   | Bit Flip Count Detection Status 7 | R               | Bit flip count detection status 7 indicates that the bit flip count in sector 7 is more than threshold bit count.  Ob: Bit flip count in sector 7 is less than the threshold.  1b: Bit flip count in sector 7 is equal to or more than the threshold bit count. |

| 6     | BFS6                                   | Bit Flip Count Detection Status 6 | R               | Bit flip count detection status 6 indicates that the bit flip count in sector 6 is more than threshold bit count.  Ob: Bit flip count in sector 6 is less than the threshold.  1b: Bit flip count in sector 6 is equal to or more than the threshold bit count. |

| 5     | BFS5                                   | Bit Flip Count Detection Status 5 | R               | Bit flip count detection status 5 indicates that the bit flip count in sector 5 is more than threshold bit count.  Ob: Bit flip count in sector 5 is less than the threshold.  1b: Bit flip count in sector 5 is equal to or more than the threshold bit count. |

| 4     | BFS4                                   | Bit Flip Count Detection Status 4 | R               | Bit flip count detection status 4 indicates that the bit flip count in sector 4 is more than threshold bit count.  Ob: Bit flip count in sector 4 is less than the threshold.  1b: Bit flip count in sector 4 is equal to or more than the threshold bit count. |

| 3     | BFS3                                   | Bit Flip Count Detection Status 3 | R               | Bit flip count detection status 3 indicates that the bit flip count in sector 3 is more than threshold bit count.  Ob: Bit flip count in sector 3 is less than the threshold.  1b: Bit flip count in sector 3 is equal to or more than the threshold bit count. |

| 2     | BFS2                                   | Bit Flip Count Detection Status 2 | R               | Bit flip count detection status 2 indicates that the bit flip count in sector 2 is more than threshold bit count.  0b: Bit flip count in sector 2 is less than the threshold.  1b: Bit flip count in sector 2 is equal to or more than the threshold bit count. |

| 1     | BFS1                                   | Bit Flip Count Detection Status 1 | R               | Bit flip count detection status 1 indicates that the bit flip count in sector 1 is more than threshold bit count.  0b: Bit flip count in sector 1 is less than the threshold.  1b: Bit flip count in sector 1 is equal to or more than the threshold bit count. |

| 0     | BFS0                                   | Bit Flip Count Detection Status 0 | R               | Bit flip count detection status 0 indicates that the bit flip count in sector 0 is more than threshold bit count.  0b: Bit flip count in sector 0 is less than the threshold.  1b: Bit flip count in sector 0 is equal to or more than the threshold bit count. |

# 4.16.4. ECC Bit Flip Count Report

The ECC Bit Flip Count Report function reports the bit flip count of each sector in a page. The users can read the bit flip count using the Get Feature command with address 40h and 50h.

Table 25 Bit Flip Count Report for Sector 0 (BFR)

| BFR3 | BFR2 | BFR1 | BFR0 | Description                                                       |

|------|------|------|------|-------------------------------------------------------------------|

| 0    | 0    | 0    | 0    | No bit flip occurred in sector 0                                  |

| 0    | 0    | 0    | 1    | 1 bit flip occurred in sector 0 and corrected                     |

| 0    | 0    | 1    | 0    | 2 bit flips occurred in sector 0 and corrected                    |

| 0    | 0    | 1    | 1    | 3 bit flips occurred in sector 0 and corrected                    |

| 0    | 1    | 0    | 0    | 4 bit flips occurred in sector 0 and corrected                    |

| 0    | 1    | 0    | 1    | 5 bit flips occurred in sector 0 and corrected                    |

| 0    | 1    | 1    | 0    | 6 bit flips occurred in sector 0 and corrected                    |

| 0    | 1    | 1    | 1    | 7 bit flips occurred in sector 0 and corrected                    |

| 1    | 0    | 0    | 0    | 8 bit flips occurred in sector 0 and corrected                    |

| 1    | 1    | 1    | 1    | Bit flips over 8 bits occurred in sector 0 and were not corrected |

Table 26 Sector Definition (BFR)

| able 20 Sector Definition (Brix) |                |       |       |          |                   |       |       |  |  |  |  |

|----------------------------------|----------------|-------|-------|----------|-------------------|-------|-------|--|--|--|--|

| BFR7                             | BFR6 BFR5      |       | BFR4  | BFR3     | BFR2              | BFR1  | BFR0  |  |  |  |  |

|                                  | Sec            | tor 1 |       | Sector 0 |                   |       |       |  |  |  |  |

|                                  |                |       |       |          |                   |       |       |  |  |  |  |

| BFR15                            | BFR14          | BFR13 | BFR12 | BFR11    | BFR10             | BFR9  | BFR8  |  |  |  |  |

|                                  | Sec            | tor 3 |       | Sector 2 |                   |       |       |  |  |  |  |

|                                  |                |       |       |          |                   |       |       |  |  |  |  |

| BFR23                            | 23 BFR22 BFR21 |       | BFR20 | BFR19    | BFR18             | BFR17 | BFR16 |  |  |  |  |

|                                  | Sec            | tor 5 |       | Sector 4 |                   |       |       |  |  |  |  |

|                                  |                |       |       |          |                   |       |       |  |  |  |  |

| BFR31                            | BFR30          | BFR29 | BFR28 | BFR27    | BFR27 BFR26 BFR25 |       |       |  |  |  |  |

|                                  | Sec            | tor 7 |       | Sector 6 |                   |       |       |  |  |  |  |

# 4.16.5. ECC Maximum Bit Flip Count Report